# **Dieter Treytnar**

Der Einfluss parasitärer Effekte in Leitungssystemen der Nanoelektronik auf die Qualität von digitalen Testmustern

### Der Einfluss parasitärer Effekte in Leitungssystemen der Nanoelektronik auf die Qualität von digitalen Testmustern

Von der Fakultät für Elektrotechnik und Informatik der Universität Hannover

zur Erlangung des akademischen Grades Doktor-Ingenieur

> genehmigte Dissertation

> > von

Dipl.-Ing. Dieter Treytnar geboren am 29. Januar 1967 in Hamm/Westfalen

**1. Referent:** Prof. Dr.-Ing. Joachim Mucha

**2. Referent:** Prof. Dr.-Ing. Hartmut Grabinski

**Tag der Prüfung:** 6. Dezember 2005

# **Danksagung**

Diese Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Theoretische Elektrotechnik und am Laboratorium für Informationstechnologie der Universität Hannover.

Mein besonderer Dank gilt meinem Doktorvater Herrn Prof. Dr.-Ing. Joachim Mucha für die Anregungen und wertvollen Hinweise zur Durchführung meiner Arbeit sowie der Bereitstellung optimaler Arbeitsbedingungen am Laboratorium für Informationstechnologie.

Für die hervorragende Betreuung, die zahlreichen fruchtbaren Diskussionen, die Möglichkeit der Forschung innerhalb seiner Abteilung am LfI sowie der Übernahme des Korreferats danke ich Herrn Prof. Dr.-Ing. Hartmut Grabinski ganz herzlich.

Weiterhin gilt mein Dank Herrn Prof. Dr.-Ing. Erich Barke für den Vorsitz der Prüfung.

Allen meinen Kollegen und studentischen Mitarbeitern am Institut für Theoretische Elektrotechnik und am Laboratorium für Informationstechnologie danke ich für die stets angenehme Zusammenarbeit. Besonderer Dank gilt dabei Michael Redeker, Markus Rudack, Faiez Ktata, Uwe Arz und Helge Kloos, sowie Prof. Dr.-Ing. T. W. Williams, der uns immer wieder zu neuen Ideen inspirierte. Viele Anregungen zu dieser Arbeit wurden in Gesprächen während der Workshops "Signal Propagation on Interconnects" gewonnen [91] - [96].

Meiner Familie und besonders meiner Frau danke ich für das Maß an Rückhalt, Verständnis und Unterstützung, das notwendig war, um das gesteckte Ziel zu erreichen.

#### Bibliografische Information Der Deutschen Bibliothek

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.ddb.de abrufbar.

ISBN 3-89963-278-8

Verlag Dr. Hut, München 2005. Sternstr. 18, 80538 München Tel.: 089/66060798 www.dr.hut-verlag.de

Die Informationen in diesem Buch wurden mit großer Sorgfalt erarbeitet. Dennoch können Fehler, insbesondere bei der Beschreibung des Gefahrenpotentials von Versuchen, nicht vollständig ausgeschlossen werden. Verlag, Autoren und ggf. Übersetzer übernehmen keine juristische Verantwortung oder irgendeine Haftung für eventuell verbliebene fehlerhafte Angaben und deren Folgen.

Alle Rechte, auch die des auszugsweisen Nachdrucks, der Vervielfältigung und Verbreitung in besonderen Verfahren wie fotomechanischer Nachdruck, Fotokopie, Mikrokopie, elektronische Datenaufzeichnung einschließlich Speicherung und Übertragung auf weitere Datenträger sowie Übersetzung in andere Sprachen, behält sich der Verlag vor.

1. Auflage 2005

©

Druck und Bindung: printy, München (www.printy.de)

# Kurzfassung

Dieter Treytnar

#### Der Einfluss parasitärer Effekte in Leitungssystemen der Nanoelektronik auf die Qualität von digitalen Testmustern

Der Test digitaler integrierter Schaltungen wird bei kleiner werdenden Strukturbreiten immer mehr zu einer Herausforderung. Galt es bisher nahezu ausschließlich die Verzögerung und die Funktion von Gattern zu überprüfen, so wird in den Nanometertechnologien der Einfluss von Verbindungsleitungen auf die Signallaufzeiten immer mehr zum dominierenden Faktor. Bussysteme aus langen parallel laufenden Leitungen, die zur Verbindung weit entfernter Funktionsblöcke verwendet werden, können selbst bei fehlerfreier Fertigung zu fehlerhafter Signalübertragung führen. Dies geschieht durch die starke Signalverzögerung und -kopplung, die trotz Verifikation und eingehaltener Entwurfsregeln oft nicht erkannt werden, da Leitungseffekte derzeit nur in geringem Maße von Designtools berücksichtigt werden.

Die vorliegende Arbeit untersucht Signale aus Testmustergeneratoren und ihre Signalintegrität in Bussystemen unter besonderer Berücksichtung der geometrischen Strukturgrössen von Leitungen in den Nanometertechnologien. Dazu werden die am häufigsten verwendeten Testmustergeneratoren (LFSR, Binärzähler, Gray Code Zähler, zellularer Automat) auf ihre Anfälligkeit gegenüber Verzögerung und Übersprechen bei der Signalübertragung über Bussysteme untersucht.

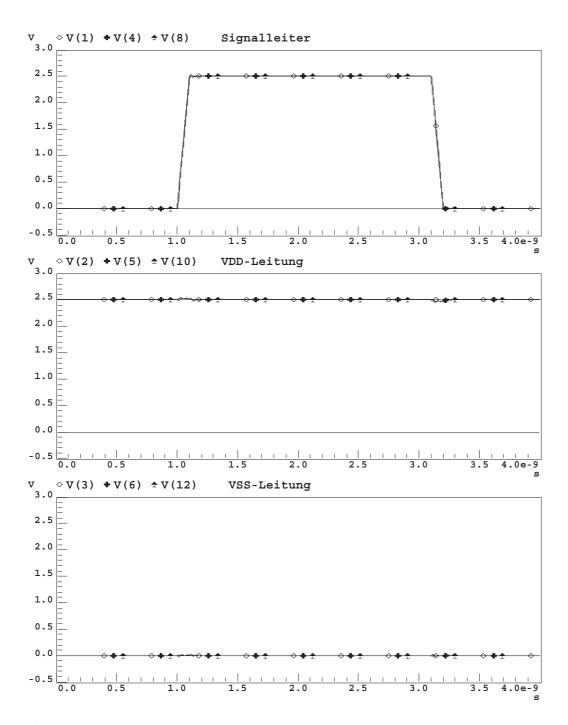

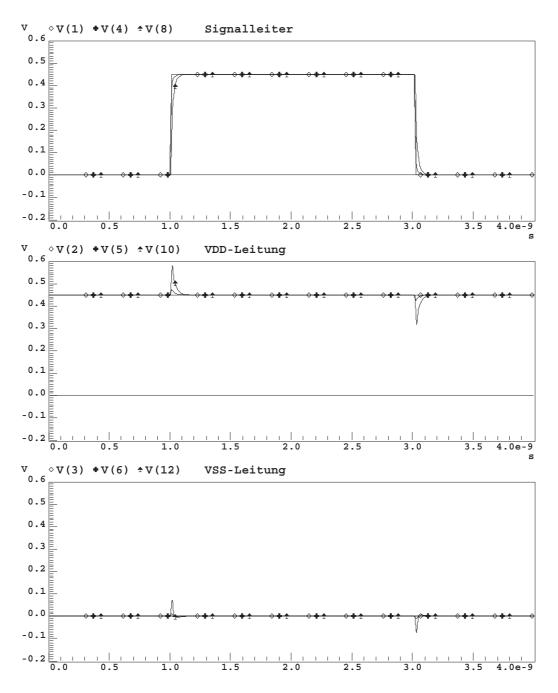

Es wird gezeigt, dass nicht nur ein Einfluß auf den Signalleitern auftritt, sondern unter bestimmten Bedingungen auch die Spannungsversorgung gestört wird. Leitungstreiber, die mit gestörter Spannung versorgt werden, propagieren die Testmuster auf den Signalleitern dann zusätzlich fehlerhaft. Dabei zeigt sich, dass die von den verschiedenen Testmustergeneratoren erzeugten Signale unterschiedlich anfällig reagieren.

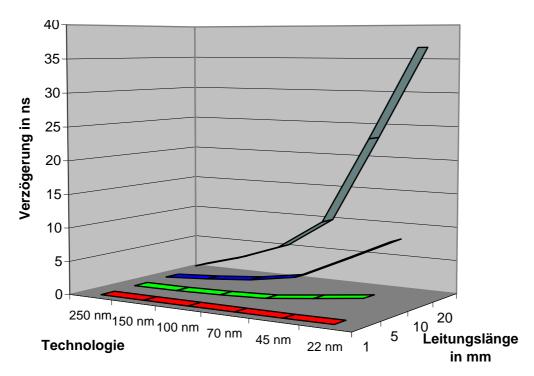

Die Untersuchungen werden für die Leitungsgeometrien in zukünftigen Technologien bis zur 22nm-Technologie durchgeführt. Dabei werden die zu erwartenden Leitungsparameter R, L und C für gekoppelte Busleitungssysteme und deren Einfluss auf die Signalübertragung dargestellt. Das Problem der zukünftigen Technologien wird nicht primär die induktive oder kapazitive Kopplung, sondern der sehr stark ansteigende Leitungswiderstand sein. Es zeigt sich, dass ab der 45nm-Technologie aufgrund der hohen Dämpfung durch den hohen Widerstandsbelags auf die Verwendung von Induktivitätsbelägen bei der Simulation weitgehend verzichtet werden kann. Diese beiden Effekte führen dazu, dass das Übertragen von Testsignalen über Leitungssysteme von 1mm Länge oder mehr ab dieser Technologie mit den untersuchten Verfahren nicht mehr möglich sein wird.

Schlagworte: Digitaltest, Testmustergeneratoren, Nanoelektronik, Leitungseffekte

### **Abstract**

Dieter Treytnar

# The influence of parasitic effects in nanometer interconnect systems on the digital test pattern quality

The test of digital integrated circuits is becoming more and more a challenge with decreasing structure sizes. Up to now, almost exclusively the delay and the function of gates were inspected; but in today's nanometer technologies the influence of interconnects on signal delays becomes more and more a dominant factor. Bus systems of long, parallel routed interconnects which are used for connecting far away functional blocks, could lead to incorrect signal transmission even with a defect-free manufacturing. This happens due to the strong signal delay and signal coupling, which are often not recognized although sufficient verification and correctly kept design rules - where these design rules usually do not consider interconnect effects yet - have been applied.

At present, applied test methods for the self-test of digital circuits produce a digital test pattern by a test pattern generator which is generally propagated via bus systems over the chip to the functional block to be tested. Even if the test pattern was produced correctly, it would falsify itself digitally by crosstalk and delay on the bus system and would no longer be useful at the far end.

In this work, the most frequently applied test pattern generators (LFSR, binary counter, Gray code counter, cellular automata) are examined for their sensitivity toward delay and crosstalk occurring at the signal transmission over bus systems.

Furthermore, it is shown that not only the signal lines are influenced, but also powerlines are disturbed under certain conditions. Bus drivers which are supplied with disturbed power additionally propagate the test patterns through the signal lines incorrectly. Besides, the signals produced by the different test pattern generators react with different susceptibility.

The experiments are carried out for the interconnect geometries of future technologies down to the 22nm-technology. Besides, the line parameters of the next years and their influence on signal transmission are presented. Interconnects and their effects will dominate signal behavior on chips in the coming years.

Keywords: digital test, test pattern generator, nanometer technology, interconnects

# Inhaltsverzeichnis

| 1 | Einl       | leitung |                                              | 1  |

|---|------------|---------|----------------------------------------------|----|

| 2 | Leit       | ungspa  | rameter in der Nanoelektronik                | 7  |

|   | 2.1        | Der K   | apazitätsbelag C'                            | 13 |

|   |            | 2.1.1   | Der Eigenkapazitätsbelag                     | 15 |

|   |            | 2.1.2   | Der Koppelkapazitätsbelag                    | 17 |

|   | 2.2        | Der In  | duktivitätsbelag L'                          | 18 |

|   |            | 2.2.1   | Der Selbstinduktivitätsbelag                 | 19 |

|   |            | 2.2.2   | Der Gegeninduktivitätsbelag                  | 21 |

|   | 2.3        | Der W   | Viderstandsbelag R'                          | 21 |

| 3 | Leit       | ungssin | nulation im Zeitbereich                      | 25 |

|   | 3.1        | Besch   | reibungsarten im Zeitbereich                 | 25 |

|   |            | 3.1.1   | Diskretes Netzwerkmodell                     | 25 |

|   |            | 3.1.2   | Verteilte Elemente                           | 27 |

|   | 3.2        | Weller  | nausbreitung auf Mehrfachleitungen           | 27 |

|   | 3.3        | Leitun  | gssimulation                                 | 28 |

|   |            | 3.3.1   | Vergleich Lossywire, RLC und RC-Simulation   | 29 |

|   |            | 3.3.2   | Induktivitäten in den Nanometer-Technologien | 32 |

| 4 | Test       | muster  | generatoren                                  | 37 |

|   | <i>1</i> 1 | 7ählar  | : für dan arschönfandan Tast                 | 30 |

xvi Inhaltsverzeichnis

|   |      | 4.1.1   | Binärzähler                                     | 40  |

|---|------|---------|-------------------------------------------------|-----|

|   |      | 4.1.2   | Gray Code Zähler                                | 41  |

|   | 4.2  | Pseudo  | ozufallsmustergeneratoren                       | 42  |

|   |      | 4.2.1   | Linear Rückgekoppeltes Schieberegister          | 42  |

|   |      | 4.2.2   | Lineare Zellulare Automaten                     | 44  |

|   | 4.3  | Vorabl  | perechnete Testmusterfolgen                     | 46  |

| 5 | Kop  | plung v | on Testmustern auf Signalleitungen              | 49  |

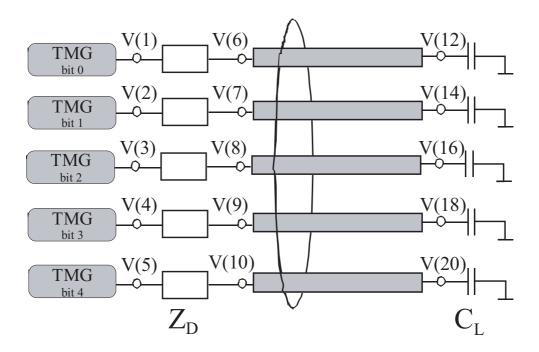

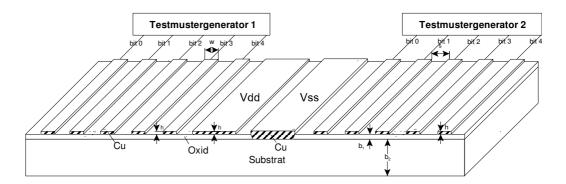

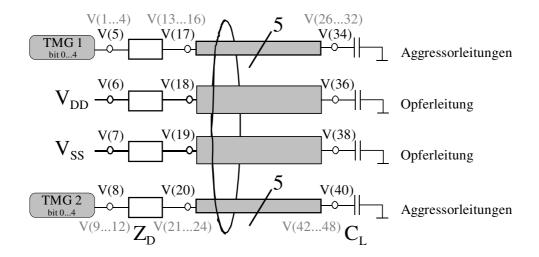

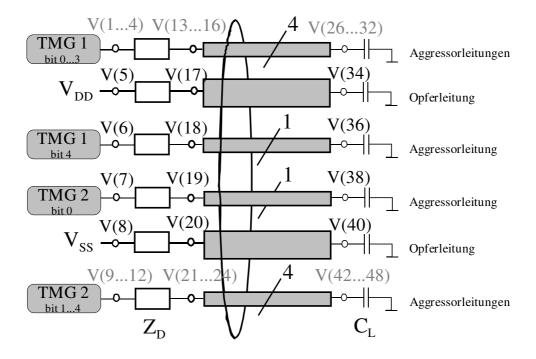

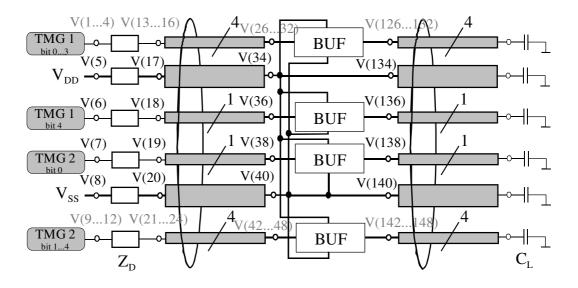

|   | 5.1  | Simula  | ationsmodelle                                   | 51  |

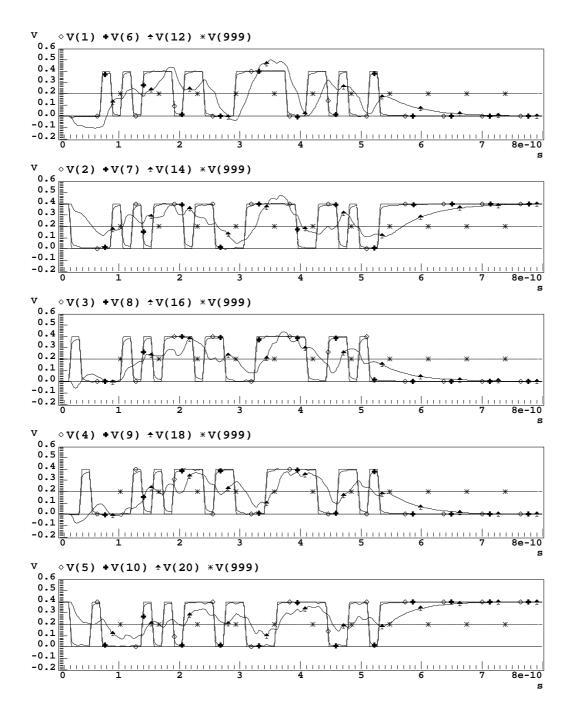

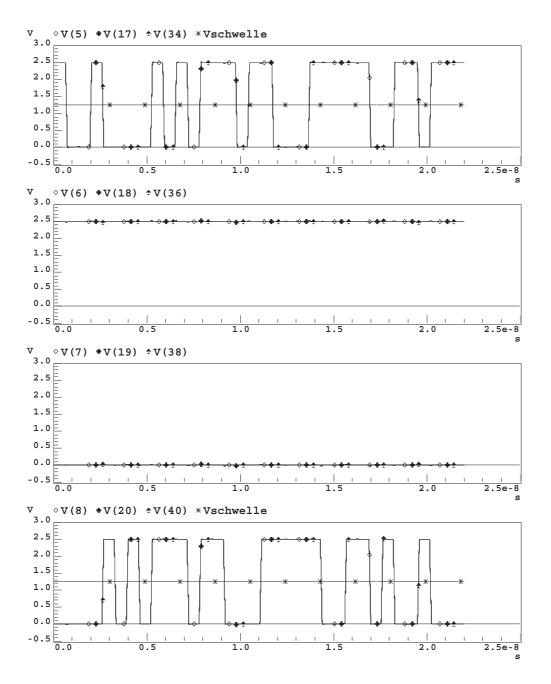

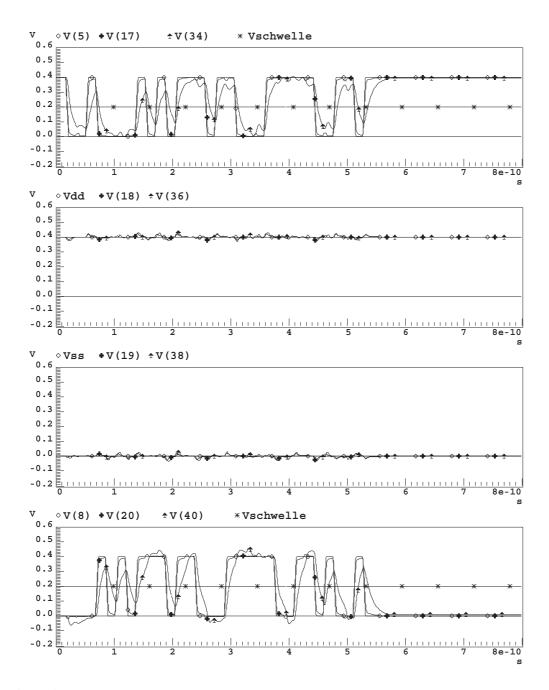

|   | 5.2  | Testmu  | uster im Sub $\mu$ -Bereich                     | 53  |

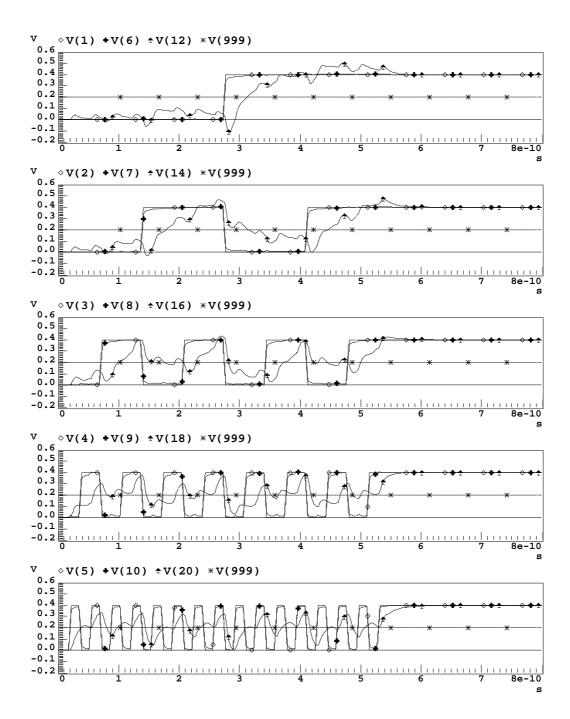

|   | 5.3  | Variati | onen der Leitungslänge                          | 59  |

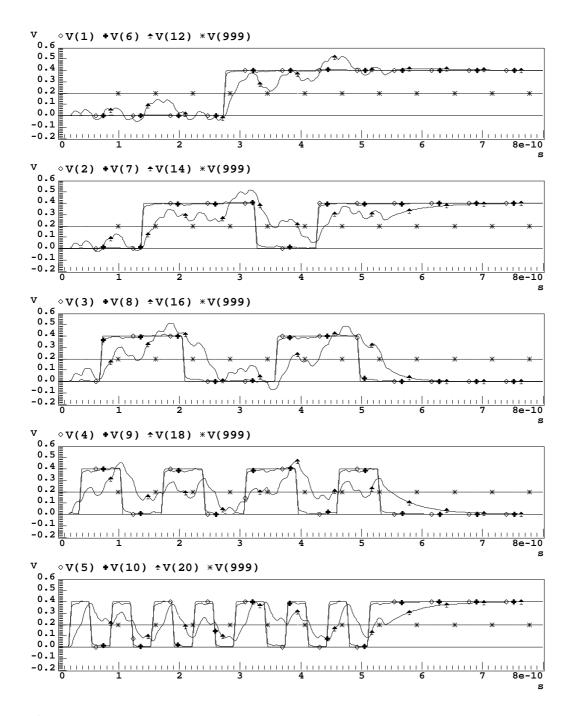

|   | 5.4  | Variati | onen des Kopplungsverhaltens                    | 62  |

|   | 5.5  | Variati | ionen der Technologie                           | 66  |

| 6 | Test | muster  | und Spannungsversorgung                         | 69  |

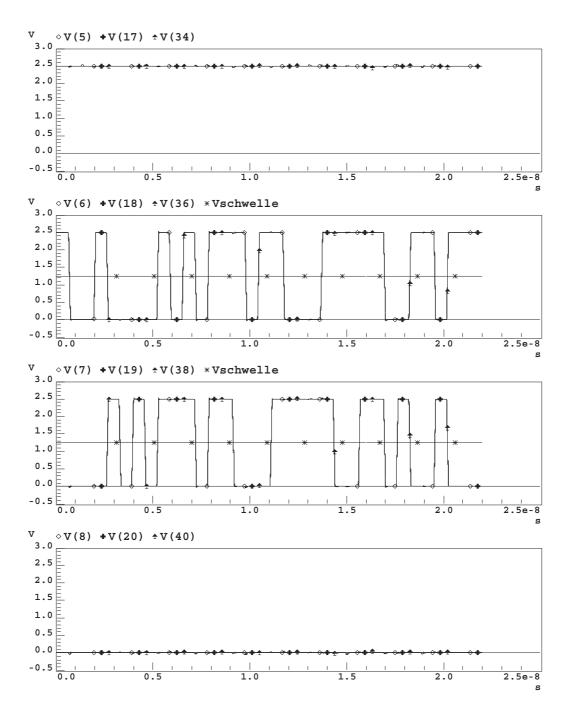

|   | 6.1  | Identis | sche Leiterbreiten                              | 71  |

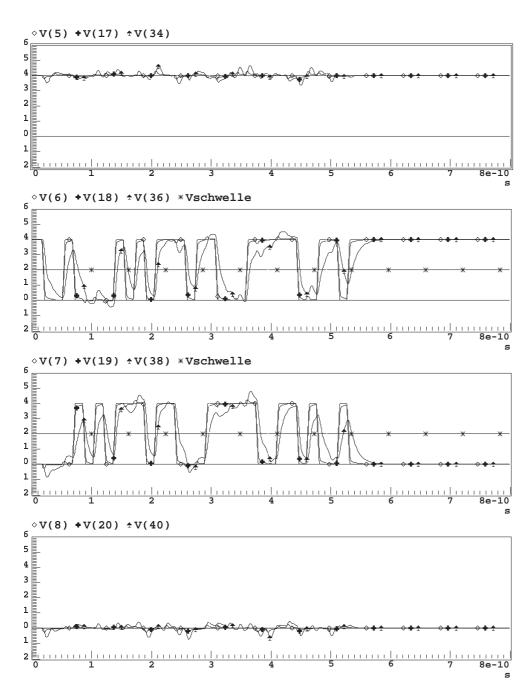

|   | 6.2  | Topolo  | ogie der Spannungsversorgung                    | 74  |

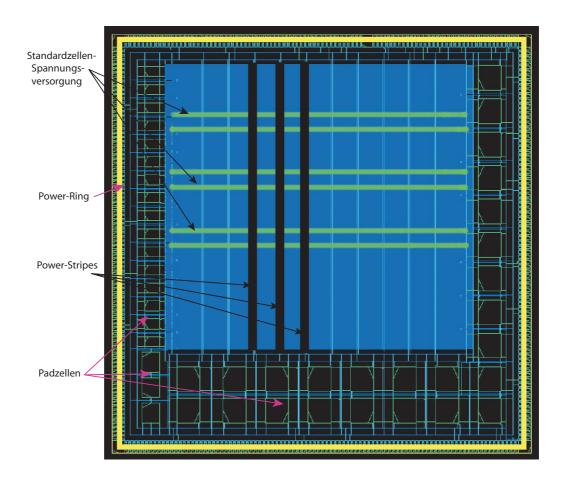

|   | 6.3  | Einfluß | ß auf die Power Stripes                         | 77  |

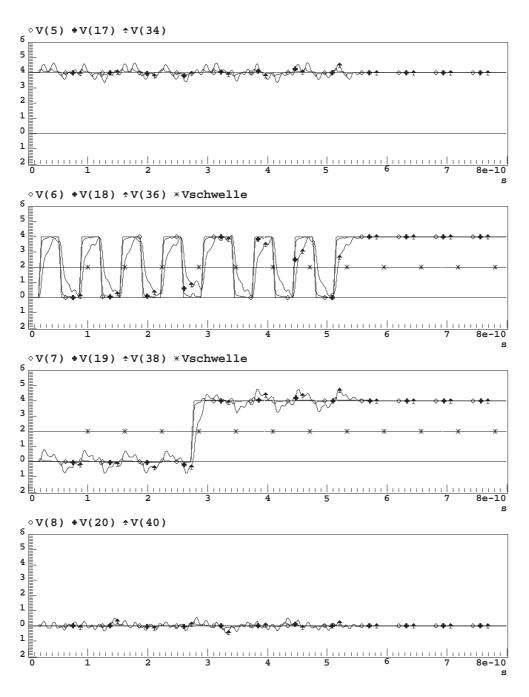

|   |      | 6.3.1   | Lineares Schieberegister                        | 78  |

|   |      | 6.3.2   | Gray Counter                                    | 81  |

|   |      | 6.3.3   | Zähler                                          | 81  |

|   |      | 6.3.4   | Zellularer Automat                              | 84  |

|   | 6.4  | Einfluß | ß auf die Versorgunsspannung für Standardzellen | 86  |

|   |      | 6.4.1   | Lineares Schieberegister                        | 88  |

|   |      | 6.4.2   | Gray Counter                                    | 88  |

|   |      | 6.4.3   | Zähler                                          | 88  |

|   |      | 6.4.4   | Zellularer Automat                              | 93  |

|   |      | 6.4.5   | Zusammenfassung                                 | 95  |

|   | 6.5  | Fehler  | übertragungsverstärkung durch Leitungstreiber   | 96  |

|   | 6.6  | Vergle  | ich der Simulationen                            | 100 |

| Inl | haltsverzeichnis                              | <u>xvii</u> |

|-----|-----------------------------------------------|-------------|

| 7   | Zusammenfassung                               | 101         |

|     | Formelverzeichnis                             | 105         |

|     | Abkürzungsverzeichnis                         | 107         |

|     | Bildverzeichnis                               | 112         |

|     | Tabellenverzeichnis                           | 113         |

|     | Literaturverzeichnis                          | 113         |

| Ar  | nhang                                         | 125         |

| A   | Vergleich Simulationen Lossywire, RLC und RC  | 127         |

| В   | Bitfehlervergleiche der Testmustergeneratoren | 131         |

| C   | Testmuster und Spannungsversorgung            | 135         |

| D   | Fehlerübertragung durch Leitungstreiber       | 137         |

# 1 Einleitung

Die zukünftigen Anforderungen an mikroelektronische Schaltungen und deren Einsatz in den Bereichen Automobiltechnik, Luft- und Raumfahrt, Telekommunikation und Computer werden durch zwei substantielle Aspekte des Chipdesigns bestimmt: Durch die wachsende Bedeutung von schnellen Daten- und Taktraten bei der Implementierung von Hochfrequenzdesigns sowie durch die Integration von Systemen. Die Idee eines integrierten, computergestützten Systemdesigns (EDA) <sup>1</sup> wird der zentrale Fokus der nächsten Jahre sein, denn nur durch diese Entwurfsmethodik wird es in Zukunft noch möglich sein, mikroelektronische Schaltungen zu entwerfen. Aufgrund der steigenden Systemkomplexität und Systemintegration muss man davon ausgehen, dass in den nächsten Jahren das Design von EMC/RF <sup>2</sup> Anwendungen problematisch wird [17].

Eines der schwierigsten Probleme in den CMOS-Nanometertechnologien (ultra deep-submicron) ist die Signalübertragung auf Leitungen und Bussystemen auf Chips (on-chip) [67]. Die rasanten Fortschritte in der Halbleiter-Technologie erlauben zwar die Fertigung von Strukturen unterhalb von 100nm, und dadurch ein sehr schnelles Schalten von Transistoren. Allerdings wird die Maximalfrequenz eines Systems durch die Leitungen mit deren stark ansteigenden Leitungswiderständen und deren parasitärer Kopplung untereinander bestimmt. Bemühungen, diesen Widerstand zu reduzieren, umfassen den Einsatz der Kupfer-Technologie statt Aluminium als Leitermaterial aufgrund des deutlich geringeren spezifischen Widerstandes von Kupfer sowie die Verwendung von hohen statt breiten Leitungen. Infolgedessen steigen jedoch die Kopplungseffekte zwischen parallelen Leitern in einer Ebene stark an. Aufgrund dieser Kopplung zwischen zwei oder mehr Signalleitern wird die Signallaufzeit bei gleichzeitigem Schalten von Signalen verkürzt (Gleichtaktschalten) oder verlängert (Gegentaktschalten) und kann daher zu einem fehlerhaften Zeitverhalten (timing) führen.

Die Beeinflussung der Leitungen untereinander kann zu fehlerhaften Logikzuständen führen, so dass sowohl die Funktion als auch der Test eines digitalen Systems nicht korrekt ist.

<sup>&</sup>lt;sup>1</sup> Electronic Design Automation

<sup>&</sup>lt;sup>2</sup> electromagnetic compatibility/radio frequency

Beim Testen von mikroelektronischen Schaltungen muss ein Testmuster fehlerfrei über Leitungssysteme bis an den Testort propagiert werden. Wird aufgrund von Leitungseffekten das Testsignal verfälscht, ist es nicht mehr als Testmuster verwendbar bzw. die Fehlererkennung wird deutlich reduziert.

Ein fehlerhaftes Testsignal entsteht z.B. dadurch, dass ein von einem Testmustergenerator erzeugtes Testmuster aufgrund von Leitungseinflüssen (Übersprechen, Crosstalk, Kopplung) gestört und damit verfälscht wird (Bitfehler). Die Störungen sind umso grösser, je dichter Leitungen beieinander liegen. Daher kommt es entscheidend darauf an, wie sich die einzelnen Bits eines Testmusters bzw. Testsignals untereinander beeinflussen. Diese Einflüsse sind umso grösser, je anfälliger ein Testsignal auf diese Störungen reagiert. So gibt es Testmustergeneratoren, die aufgrund ihrer Struktur Testmuster so erzeugen, dass sich Nachbarleitungen gegenseitig stark beeinflussen. Andere Testmustergeneratoren wiederum erzeugen Muster, die besonders immun gegen Störungen untereinander sind. Schliesslich gibt es noch Testmustergeneratoren, die Muster erzeugen, die je nach Beschaltung auf Bussystemen freundliche oder auch unfreundliche Nachbarn besitzen.

Aber nicht nur die Signalleiter untereinander sind von diesen Effekten betroffen, sondern Testmuster können auch die Versorgungsleitungen so stören, dass die Spannung auf der Leitung, mit der die mikroelektronische Schaltung mit Betriebsspannung versorgt wird, einbricht. Besonders bei der Spannungsversorgung von Standardzellen (siehe Kap. 6.4) und bei sogenannten Power Stripes (siehe Kap. 6.2) kann dieser Einfluss so stark sein, dass die im Bussystem integrierten Treiber und Gatter aufgrund des Spannungseinbruches nicht mehr korrekt funktionieren. Dies führt nicht nur zu Fehlverhalten im Systembetrieb sondern auch dazu, dass ein zu propagierendes Testmuster zusätzlich verfälscht wird.

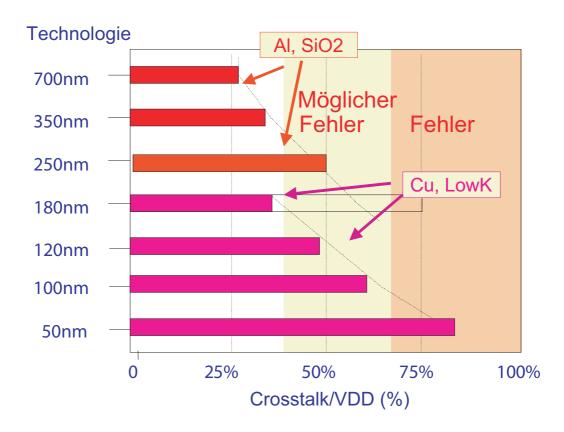

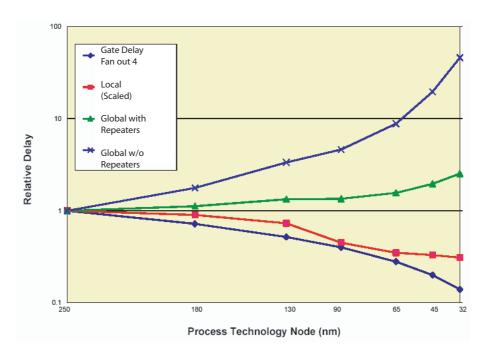

Eine Kopplung tritt selbstverständlich auch zwischen Leitern aus unterschiedlichen Materialen auf wie in [81] gezeigt wird. Eine technologische Lösung gegen Übersprechen ist daher die Verwendung spezifischer dielektrischer Materialien (Low-K) bei kleineren Technologien zur Reduzierung der Koppelkapazität. Das Problem des Übersprechens wird auch aufgrund der in [55] gezeigten technologischen Grenzen in Zukunft eine der wichtigsten zu lösenden Aufgabe sein. Bild 1.1 zeigt für verschiedene Technologien das maximale Übersprechen bei gekoppelten Leitungen abhängig vom Verhältnis Crosstalk/Betriebsspannung. Durch die Einführung von Low-K Materialien bzw. Kupfer wurde das mögliche Auftreten eines Fehlers bei der Signalübertragung verringert. Aufgrund höherer Taktraten und geringen Leiterabständen wird jedoch in naher Zukunft Crosstalk dennoch zunehmend an Bedeutung gewinnen.

**Bild 1.1:** Übersprechen bei gekoppelten Leitungen [42]

Ansätze mit veränderten Design-Regeln und grösseren geometrischen Abmessungen wie in [82] vermeiden zwar ein Übersprechen, vergrößern jedoch auch die verwendete Chipfläche. Die grundsätzliche Ursache für das Auftreten von solchen Effekten wird damit aber nicht behoben.

Ansätze wie in [46] und [54] dargestellt, reduzieren durch den Einbau von geeigneten Treibern die Leitungsverzögerung auf Bussystemen. Eine Übersicht über die Erfolge bei der Verhinderung von Kopplung in den letzten Jahren ist in [97] zu finden.

Aus der Sicht des Designers könnte der Effekt des Übersprechens toleriert werden, wenn lange, parallele Leitungen vermieden werden. Dazu werden spezielle Design Flows entwickelt, die besonders die Schwierigkeiten der Signalintegrität berücksichtigen [26]. Tatsächlich ist es aber erforderlich, die maximale Leitungslänge bei jeder Technologie durch Messungen oder Simulationen zu bestimmen.

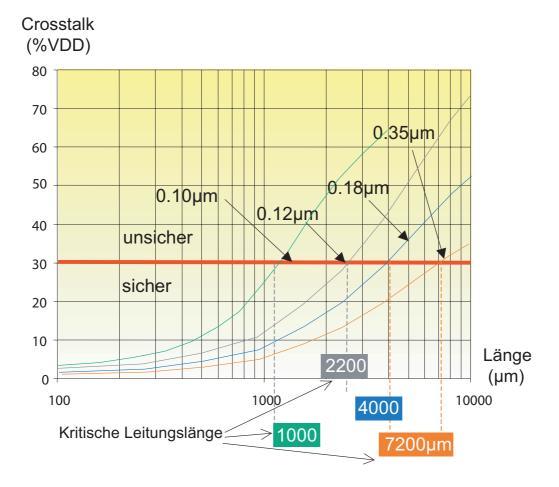

Die kritische Leitungslänge wird als obere Begrenzung in Routing-Design-Tools fest eingestellt, um sicherzustellen, dass keine Leitung länger als das zulässige Limit, bei dem ein Übersprechen bzw. eine zu grosse Verzögerung auftritt,

ist. Bild 1.2 zeigt die Entwicklung der kritischen Leitungslänge für verschiedene Technologien, bei denen Übersprechen und Kopplung bis zu 30 % der Versorgungsspannung VDD auftreten kann, ohne dass das System unsicher wird. Die kritische Leitungslänge hat sich im Laufe der Zeit von 8mm in der 350nm Technologie bis zu 1mm in der 100nm Technologie verringert.

In den zukünftigen Nanometertechnologien <sup>3</sup> ist davon auszugehen, dass sich diese kritische Länge bis auf 0,3mm in der 22nm Technologie reduziert [12], [29], [30], [44], [98], [99].

**Bild 1.2:** Kritische Leitungslänge für sicheres Schalten [42]

<sup>&</sup>lt;sup>3</sup> Chipdesigner sprechen bei Technologien im zweistelligen Nanometerbereich (99nm und kleiner) nicht mehr von Mikro-, sondern von Nanoelektronik und somit von Nanometertechnologien.

Die Probleme, die aus dieser kritischen Leitungslänge für das Testen entstehen, sind noch kaum untersucht. Lediglich in wenigen Veröffentlichungen wird diese Problematik angesprochen [8], [14], [20], [21], [24]. Während es etliche Veröffentlichungen über Testverfahren zur Ermittlung von leitungsbedingten Fehlern (vor allem Kopplung) in Schaltungen gibt [9], [14], [21], [22], [23], [60], [62], [84], [108] sind nahezu keine Untersuchungen über die Anfälligkeit von Testmustern in Bussystemen auf Chips durchgeführt worden. Dabei besteht gerade hier Bedarf, da zukünftige mikroelektronische Schaltungen mit mehreren Millionen von Transistoren [34] mit vertretbarem Aufwand nur noch mit Hilfe von Selbsttestverfahren getestet werden können [83], [109], wobei diese Testmuster fehlerfrei über lange Bussysteme propagiert werden müssen.

In Kapitel 2 werden zunächst das Verhalten und der Trend der Leitungsparameter in den Nanometertechnologien gezeigt. Die Grundlagen und die verschiedenen Möglichkeiten der Leitungssimulation werden in Kapitel 3 erläutert. Kapitel 4 beschreibt das Prinzip des Testens mit Testmustergeneratoren und stellt die in dieser Arbeit untersuchten Generatoren vor. Das Verhalten von Kopplung auf Signalleitern bei verschiedenen Randbedingungen wird in Kapitel 5 dargestellt. Der Einfluss der Testmustersignale auf die Spannungsversorgung wird in Kapitel 6 gezeigt. Eine Zusammenfassung sowie Anregungen für weiterführende Arbeiten zeigt Kapitel 7.

<u>6</u> <u>EINLEITUNG</u>

# 2 Leitungsparameter in der Nanoelektronik

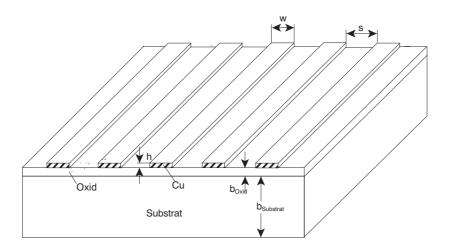

Die zunehmende Miniaturisierung der Strukturen in den Nanometertechnologien macht auch nicht vor den Geometrien der Verbindungsleitungen auf mikroelektronischen Schaltungen halt [89], [90]. Während in der 130nm Technologie Strukturen mit minimaler Leitungsbreite von ca.  $0.34\mu m$  und mit minimaler Leitungshöhe von  $0.67\mu m$  in der obersten Metall-Lage gefertigt wurden, werden diese Geometrien bis zur 22nm Technologie, die laut SIA Roadmap [7], [50] im Jahr 2016 aktuell sein wird, nur noch ca. 20 % dieser Abmessungen besitzen. Die Leitungsbreite in dieser Technologie wird lediglich bis zu  $0.05 \mu m$ , die Leiterhöhe nur noch 0,13μm betragen. Dazu reduziert sich der minimale Abstand der Leitungen von  $0.34\mu m$  in der 130nm Technologie auf  $0.05\mu m$  in der 22nm Technologie und der vertikale Abstand der obersten Metall-Lagen von  $1,20\mu$ m auf  $0,85\mu$ m. Diese Verkleinerung der Leitungsquerschnitte führt zu einer starken Veränderung der Leitungseigenschaften [3]. Ein zusätzlicher starker Anstieg der Taktfrequenz auf nahezu 30 GHz und eine Reduzierung der Betriebsspannung auf 0,4 Volt führen zu einer dramatischen Beeinflussung der Transmissionseigenschaften von Leitungen [38]. In Kapitel 5 werden diese Effekte durch Simulationen aufgezeigt.

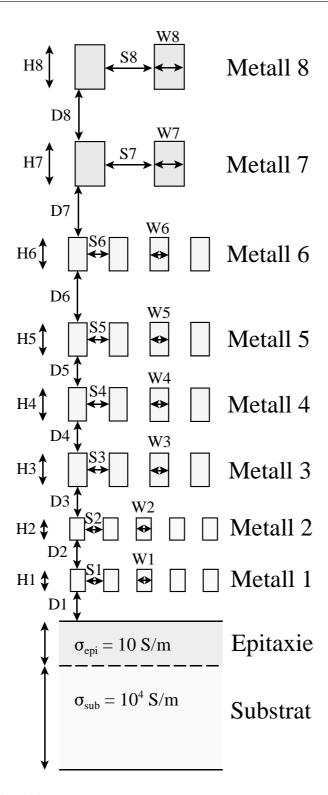

Bild 2.1 zeigt zusammen mit Tabelle 2.1 die von der SIA Roadmap prognostizierten Leitergeometrien in den zukünftigen Technologien. Werte, die nicht direkt aus der Roadmap abzulesen sind, wurden aus vorangegangen Untersuchungen interpoliert [5] und durch Messungen [4], [6], [104], [105] bestätigt.

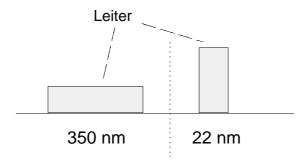

Bild 2.1: Vereinfachte Chip-Querschnitts-Geometrie

| Technologie         | 130 nm | 115 nm | 100 nm | 90 nm | 80 nm | 70 nm | 65 nm | 45 nm | 32 nm | 22 nm |

|---------------------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Jahr                | 2001   | 2002   | 2003   | 2004  | 2005  | 2006  | 2007  | 2010  | 2013  | 2016  |

| W1, W2 [µm]         | 0,18   | 0,15   | 0,12   | 0,11  | 0,09  | 0,09  | 0,08  | 0,05  | 0,04  | 0,03  |

| W3 - W6 [µm]        | 0,23   | 0,19   | 0,16   | 0,13  | 0,12  | 0,11  | 0,10  | 0,07  | 0,05  | 0,03  |

| W7, W8 [µm]         | 0,34   | 0,28   | 0,24   | 0,23  | 0,18  | 0,16  | 0,15  | 0,10  | 0,07  | 0,05  |

| S1, S2 [µm]         | 0,18   | 0,15   | 0,12   | 0,11  | 0,09  | 0,09  | 0,08  | 0,05  | 0,04  | 0,03  |

| S3 - S6 [µm]        | 0,23   | 0,19   | 0,16   | 0,13  | 0,12  | 0,11  | 0,10  | 0,07  | 0,05  | 0,03  |

| S7, S8 [µm]         | 0,34   | 0,28   | 0,24   | 0,23  | 0,18  | 0,16  | 0,15  | 0,10  | 0,07  | 0,05  |

| H1, H2 [µm]         | 0,28   | 0,24   | 0,20   | 0,18  | 0,16  | 0,14  | 0,13  | 0,09  | 0,07  | 0,05  |

| H3 - H6 [µm]        | 0,36   | 0,30   | 0,27   | 0,23  | 0,20  | 0,18  | 0,18  | 0,12  | 0,09  | 0,07  |

| H7, H8 [µm]         | 0,67   | 0,57   | 0,50   | 0,48  | 0,40  | 0,35  | 0,32  | 0,24  | 0,17  | 0,13  |

| D1, D2 [μm]         | 0,70   | 0,70   | 0,70   | 0,66  | 0,63  | 0,60  | 0,58  | 0,56  | 0,54  | 0,51  |

| D3 - D5 [μm]        | 0,66   | 0,66   | 0,66   | 0,63  | 0,60  | 0,57  | 0,53  | 0,50  | 0,47  | 0,43  |

| D6 - D8 [μm]        | 1,20   | 1,20   | 1,20   | 1,10  | 1,05  | 1,00  | 0,95  | 0,93  | 0,90  | 0,85  |

| Epitaxiedicke [µm]  | 0,5    | 0,465  | 0,435  | 0,4   | 0,365 | 0,335 | 0,3   | 0,3   | 0,25  | 0,2   |

| Substratdicke [µm]  | 400    | 400    | 400    | 400   | 400   | 400   | 400   | 400   | 400   | 400   |

| Frequenz [GHz]      | 1,7    | 2,3    | 3,1    | 4     | 5,2   | 5,6   | 6,7   | 11,5  | 19,3  | 28,8  |

| Rise/Fall Zeit [ns] | 0,088  | 0,065  | 0,048  | 0,038 | 0,029 | 0,027 | 0,022 | 0,013 | 0,008 | 0,005 |

| Halbtakt [ns]       | 0,294  | 0,217  | 0,161  | 0,125 | 0,096 | 0,089 | 0,075 | 0,043 | 0,026 | 0,017 |

| Clast [pF]          | 0,015  | 0,013  | 0,01   | 0,009 | 0,008 | 0,007 | 0,007 | 0,005 | 0,003 | 0,002 |

| Vdd (V)             | 1,1    | 1      | 1      | 1     | 0,9   | 0,9   | 0,7   | 0,6   | 0,5   | 0,4   |

| epsilon r           | 3,6    | 3,6    | 3,6    | 3,1   | 3,1   | 3,1   | 2,7   | 2,1   | 1,9   | 1,8   |

**Tabelle 2.1:** Geometrische Daten von Leitungen auf Basis der SIA Roadmap [7]

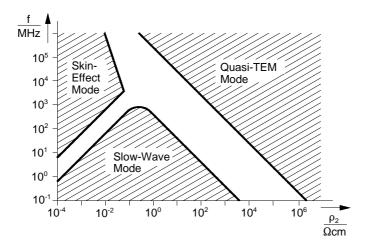

Für die Simulation von Leitbahneffekten ist es sinnvoll, die geometrische Struktur der Leitung sowie die Materialeigenschaften in Form von Leitungsparametern abzubilden. Die wichtigsten Parameter sind in erster Linie der Widerstandsbelag R' und der Kapazitätsbelag C', aber auch gerade bei hochfrequenten Schaltungen (1 GHz und höher) kann der Induktivitätsbelag L' eine wichtige Rolle spielen. Der Leitwertsbelag G' repräsentiert die Verluste, die aufgrund von Querströmen im Substrat entstehen. Das derzeit bei der Fertigung mikroelektronischer Schaltungen am Häufigsten verwendete Siliziumsubstrat ist i.A. recht gut leitend. Daher wurden in dieser Arbeit Untersuchungen von Leitungen auf hochleitendem Silizium-Substrat ( $\rho_2 = 10^{-4} \Omega cm$  bzw.  $\sigma_{sub} = 10^4 S/m$  mit  $\sigma_{sub} = 1/\rho_2$ ) mit Epitaxieschicht bei ebenfalls hohen Frequenzen (1 GHz und höher) durchgeführt. Die Wellenausbreitung erfolgt somit im Bereich des Skin-Effekt-Modes (Bild 2.2). Das Bild zeigt die Frequenz aufgetragen über dem spezifischen Substratwiderstand. Unter bestimmten Annahmen bei den Schichtdicken ergeben sich die im Bild dargestellten Bereichsgrenzen. In diesem Mode kann die Leitwertsmatrix häufig vernachlässigt werden, da die dissipierte Leistung  $P_R \gg P_G$  ist (Erläuterung siehe [35]).

Bei den Simulationen in den nachfolgenden Kapiteln werden daher die Leitungen in sehr guter Annäherung an die Realität nur über die Leitungsparameter R', L' und C' beschrieben.

**Bild 2.2:** Graphische Darstellung der auftretenden Ausbreitungsmoden nach Hasegawa [43]

Die exakte Berechnung der Leitungsbeläge lässt sich in der Regel für die gebräuchlichen, einigermaßen komplexen Geometrien nur mit Hilfe numerischer Feldberechnungen durchführen und ist dadurch meist sehr zeit- und rechenintensiv. Reduziert man die Betrachtungsweise jedoch auf zweidimensionale Strukturen (aufgrund der Homogenität in Längsrichtung ist dies für hinreichend lange Leitbahnen zulässig), so lässt sich die Berechnungszeit der Parameter erheblich verringern. Die Parameter für die Untersuchungen in dieser Arbeit wurden mit dem am Laboratorium für Informationstechnologie entwickelten Programm LI-PACIFIC [41] extrahiert. Dieses Programm basiert auf einer quasianalytischen Methode zur Berechnung der Leitungsparameter zweidimensionaler Geometrien. Bei Validierung der Ergebnisse zeigte sich, dass die Genauigkeit dieses Tools bei den hier verwendeten Strukturen dem Vergleich mit FEM-Simulationen durchaus standhält [13].

In den folgenden Kapiteln wird die Veränderung der Leitungsparameter pro Länge R', L' und C' in den zukünftigen Technologien gezeigt. Dabei wird nur oberflächlich auf die genaue Definition und mathematische Beschreibung der Leitungsbeläge eingegangen. Eine exakte und ausführliche Formulierung der Leitungsbeläge findet sich in [79].

Heutige Chips werden nahezu ausschliesslich mit Kupferleitern gefertigt. Leiter, die mit der alten Aluminiumtechnologie gefertigt werden, besitzen einen um Faktor 2 höheren Widerstandsbelag. Dies bedeutet, dass die Leitungsverzögerung höher ist als die von Leitern aus Kupfer. Da die Effekte bei Kupferleitern schon ausreichen, um die Probleme zukünftiger Technologien zu zeigen und Aluminiumleiter in Kürze nicht mehr gefertigt werden, wird auf eine Darstellung von

Simulationen mit Aluminiumleitern verzichtet. Für die Untersuchungen in die-

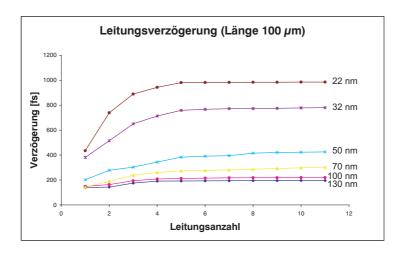

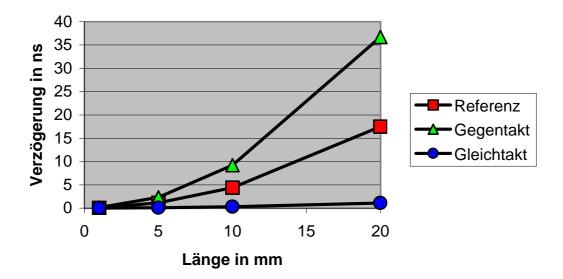

**Bild 2.3:** Schematische Struktur des verwendeten 5-Leiter-Systems

ser Arbeit wird eine schematische Chip-Struktur mit 5 parallel in einer Metallebene geführten Leitern (Bild 2.3) zugrundegelegt. Die SIA Roadmap prognostiziert einen Anstieg von derzeit 8 Metallebenen auf bis zu 11 Metallebenen in der 22nm Technologie. Um die Ergebnisse in den verschiedenen Technologien vergleichen zu können, werden in allen Technologien 8 Metallebenen zugrunde gelegt (Bild 2.1). Die Metallebene 1 ist immer die unterste Ebene, die Ebenen 4, 5 und 6 sind mittlere Ebenen und die Metallebene 8 die oberste Ebene (deren geometrische Werte bei einer höheren Anzahl von Metallebenen den Ebenen 9, 10 bzw. 11 entsprechen). Mit Hilfe des Extraktionsprogramms LIPACIFIC werden die Leitungsparameter extrahiert mit der Randbedingung, dass die unendlich gut leitenden Rückleiter des Leitungssystems jeweils rechts und links parallel zu den Signalleitern sehr weit entfernt angeordnet und mit dem Substrat verbunden sind [63]. Die Verwendung eines 5-Leiter-Systems wird dadurch begründet, dass sich die Leitungsverzögerung der hier verwendeten Geometrien bei Systemen mit mehr als 5 parallelen Leitungen nicht mehr signifikant ändert und daher die Betrachtung eines Systems mit 5 Leitern ausreicht. Dazu wurden Simulationen bei verschiedenen Technologien durchgeführt mit Leitungssystemen gleicher Länge und unterschiedlicher Leiteranzahl. Bild 2.4 zeigt die Leitungsverzögerung auf der bzw. einer mittleren Leitung. Es zeigt sich, dass bei 5 Leitungen eine gewisse Sättigung bei der Verzögerungszeit auftritt. Das Hinzufügen von weiter entfernten Nachbarleitungen führt zu keinem nennenswerten Anstieg der Verzögerungszeit mehr. Für die Kopplung von Nachbarleitungen sind daher nur die beiden nächsten Nachbarn jeweils rechts und links einer Leitung entscheidend - die Koppeleffekte durch weiter entfernte Leitungen können vernachlässigt werden, da sie außer bei

magnetischen Koppeleinflüssen keinen Einfluss mehr auf die Signalverzögerung besitzen.

**Bild 2.4:** Signalverzögerung in Abhängigkeit der Leiteranzahl

Globale und damit lange Verbindungsleitungen (in der Literatur auch als Inter-Modul/core bezeichnet) werden meist in den obersten Metallebenen angeordnet (in der verwendeten beispielhaften Struktur also Metall-Lagen 7 und 8). Die mittleren Metallebenen sind als Verdrahtungsebenen zur Verbindung von globalen und lokalen Leitungen (Intra-Modul/core) vorgesehen (hier Metall-Lagen 3 - 6). Kurze lokale Leitungen werden im Normalfall in den unteren Metallebenen gefertigt (Metall-Lagen 1 und 2).

Leitungsparameter verändern sich jedoch bei einer gegebenen Geometrie aufgrund des Skin-Effektes im Substrat frequenzabhängig (der Skin Effekt im Leiter kann aufgrund der kleinen Leiterquerschnitte vernachlässigt werden) und zeigen das folgende Verhalten: der Widerstandsbelag eines Leiters wird mit steigender Frequenz grösser, der Induktivitätsbelag wird kleiner, da die innere Induktivität gegen Null geht, wobei hier das Magnetfeld im Substrat mit zu berücksichtigen ist ( $L_{ges} = L_i + L_a$ ). Der Kapazitätsbelag bleibt aufgrund der hohen Substratleitfähigkeit nahezu konstant ([35], [13], [37]). In dieser Arbeit wurde nicht die Frequenzabhängigkeit von Leitungsparametern untersucht, sondern die Parameter bei der von der SIA Roadmap zur jeweiligen Technologie prognostizierten maximalen Taktfrequenz extrahiert. Ein Vergleich von Simulationsergebnissen des Zeitbereichssimulators LOSSYWIRE mit einem Simulator, der frequenzabhängige Parameter berücksichtigt [13], zeigt, dass diese Vereinfachung durchaus zulässig ist: Dazu wurde ein Leitungssystem mit einem Impulssignal beaufschlagt und das Signal am Ende des Leitungssystems beobachtet. Die Simulation mit 81

frequenzabhängigen Parametern lieferte nahezu das gleiche Ausgangssignal wie die Simulation mit einem lediglich bei einer angenommenen maximalen Frequenz des Signales extrahiertem Parametersatz [37].

### 2.1 Der Kapazitätsbelag C'

Den Kapazitätsbelag C' definiert man als die Kapazität C pro Länge als Ladung, die ein Leiter gegenüber allen anderen Leitungen und dem Substrat besitzt. Für die Maxwellschen Kapazitätskoeffizienten gilt definitionsgemäß:

$$q_i = \sum c_{ik} V_k$$

oder in Matrixform

$$\begin{pmatrix} q_1 \\ q_2 \\ \vdots \\ q_n \end{pmatrix} \cdot = \begin{pmatrix} c_{11} & c_{12} & \cdots & c_{1n} \\ c_{12} & c_{22} & \cdots & c_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ c_{1n} & c_{2n} & \cdots & c_{nn} \end{pmatrix} \begin{pmatrix} V_1 \\ V_2 \\ \vdots \\ V_n \end{pmatrix}$$

Die Matrix enthält die Maxwellschen Kapazitätskoeffizienten  $c_{nn}$  und ist immer symmetrisch.

Durch die Beziehungen

$$C_{kn} = -c_{kn}$$

mit  $n \neq k$

sowie

$$C_{kk} = \sum_{n=1}^{k} c_{kn}$$

lassen sich die Teilkapazitäten  $C_{nn}$  berechnen.

Für die Abschätzung des Teilkapazitätsbelages einer Einzelleitung über dem Substrat gelingt es noch, eine Näherungsformel anzugeben. Dabei gilt für eine Leitung mit der Breite W, der Höhe H auf einer dielektrischen Schicht der Dicke D näherungsweise [88]:

$$\frac{C_1}{\varepsilon_{ox}} = 1.15 \frac{W}{D} + 2.80 \frac{H^{0.222}}{D}$$

Für Zweileitersysteme über dem Substrat wurde 1992 eine ähnliche Näherung nach [25] vorgestellt (S ist der Abstand zwischen den Metall-Leitern):

$$\frac{C_{10}}{\varepsilon_{ox}} = \frac{W}{D} + 3,28 \left(\frac{H}{H + 2D}\right)^{0,023} + \left(\frac{S}{S + 2D}\right)^{1,16}$$

üb

(Kapazität gegenüber Masse, Substrat ist geerdet)

bzw.

$$\frac{C_{12}}{\varepsilon_{ox}} = \frac{W}{H} + 1,064 \left(\frac{T}{S}\right) \left(\frac{T + 2H}{T + 2H + 0,5S}\right)^{0,695}$$

$$+ \left(\frac{W}{W + 0,8S}\right)^{1,4148} \left(\frac{T + 2H}{T + 2H + 0,5S}\right)^{0,804}$$

$$+ \left(\frac{W}{W + 0,8S}\right)^{0,055} \left(\frac{2H}{2H + 0,5S}\right)^{3,542}$$

(Kapazität zwischen zwei benachbarten Leitungen, Substrat ist geerdet)

Eine analytische Berechnung der Leitungsparameter von n-Leiter-Systemen mit Hilfe von Näherungsformeln ist i.a. nicht möglich. Hierfür sind numerische Verfahren notwendig.

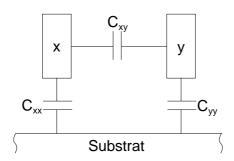

In n-Leiter-Systemen unterscheidet man zwischen der Kopplung gegenüber Masse  $C'_{kk}$  (k=1,...,n) - auch Eigenkapazität genannt - und der Kopplung zwischen benachbarten Leitern  $C'_{ki}$   $(k=1,...,n), (i=1,...,n), k \neq j$  - dem Koppelkapazitätsbelag (Bild 2.5).

**Bild 2.5:** Teilkapazitäten eines Zweileitersystems

Ferner soll in dieser Arbeit die mit der Technologie kleiner werdende Dielektrizitätskonstante  $\varepsilon_r$  des Dielektrikums zwischen den Metallebenen betrachtet werden. Ging man bisher davon aus, dass die Dielektrizitätskonstante sich mit kleiner werdenden Technologien nicht oder nur wenig ändert, so prognostiziert die SIA Roadmap (Tabelle 2.1) ein stetiges Absinken von  $\varepsilon_r$ . Während in der 180nm Technologie  $\varepsilon_r$  ca. 3,7 betrug, so setzte sich der Trend in der 130nm Technologie

mit  $\varepsilon_r = 2,6$  bis 3,0 fort. Die SIA skaliert daher für die zukünftigen Technologien ebenfalls die Dielektrizitätskonstante des Dielektrikums. Da sich die Kapazität von Leitungssystemen bei diesen Geometrien und einer bestimmten Leitfähigkeit proportional zur Dielektrizitätskonstante ergibt, werden die Kapazitäten mit den kleineren Technologien bei fallendem  $\varepsilon_r$  ebenfalls geringer (siehe Kapitel 2.1).

In älteren Technologien (350nm und grösser) war die Breite der Leitungen grösser als deren Höhe (Bild 2.6) - d.h. die Kapazität gegenüber Masse war i.a. grösser als

**Bild 2.6:** Vergleich Leitergeometrie 350nm/22nm Technologie

die Koppelkapazität zwischen benachbarten Leitungen (unter Berücksichtigung der Leiterabstände). Seit der 250nm Technologie und darunter hat sich dieses umgekehrt: Leiter sind heutzutage höher als breit. So hat sich zwar die Kapazität gegen Masse reduziert, jedoch die Koppelkapazität zwischen Nachbarleitern hat sich stark erhöht. Somit besitzt in zukünftigen Technologien die Koppelkapazität einen wesentlich stärkeren Einfluss auf das Signalverhalten auf Leitungen als die Eigenkapazität.

#### 2.1.1 Der Eigenkapazitätsbelag

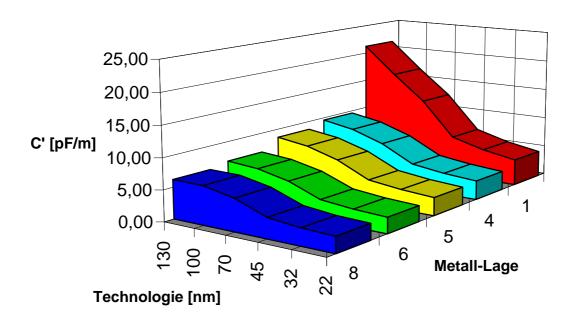

Bild 2.7 zeigt das Verhalten des Eigenkapazitätsbelages (Kapazität gegenüber dem geerdeten Substrat)  $C_{33}'$  (Mittelleiter) bei dem 5-Leitersystem in 5 ausgewählten Metallebenen. Durch die geometrische Anordnung der Leiter in den verschiedenen Metallebenen reduziert sich die Eigenkapazität in der dem Substrat am nächsten liegenden Metallebene 1 von der 130nm Technologie zur 22nm Technologie um Faktor 5. In der dem Substrat entferntesten Metallebene 8 ist die Verringerung dagegen lediglich etwas mehr als Faktor 2. Auf die dazwischenliegenden Metallebenen trifft dieses ebenfalls zu: je weiter entfernt die Metallebene vom Substrat ist, desto geringer ist die Änderung der Eigenkapazität bei kleineren Geometrien (zum Vergleich: Metallebene 6: Faktor 2,7, Metallebene 5: Faktor 3, Metallebene

**Bild 2.7:** Eigenkapazitätsbelag der mittleren Leitung eines 5-Leitersystems

4: Faktor 3,1). Dies lässt sich einfach mit Hilfe von Bild 2.1 erklären: Die Leiterbreite wird über alle Metallebenen mit der Technologie deutlich kleiner, jedoch nimmt der Abstand der untersten Metallebene 1 zum Substrat mit kleiner werdender Technologie kaum ab. Im Gegensatz dazu wird der Substratabstand der oberen Metallebenen deutlich geringer. Geht man in erster Näherung von der Gleichung

$$C = \varepsilon \frac{A}{d}$$

,  $w \gg d$  (A: Leiterquerschnitt, d: Substratabstand, w: Leiterbreite)

aus, so ändert sich der Leiterquerschnitt A mit kleiner werdenden Technologien über alle Metallebenen in ähnlicher Weise, jedoch der Abstand d zum Substrat bleibt in Metallebene 1 i.a. konstant und ändert sich stark in höher liegenden Metallebenen. Somit ist die Grösse der Eigenkapazität bei globalen Leitungssystemen (Verdrahtung in Metallebenen 7 und 8) mit Verkleinerung der Technologie nahezu konstant, da sich Querschnitts- und Abstandsverkleinerung nahezu aufheben. Dazu kommt, dass  $\varepsilon_r$  mit kleiner werdenden Technologien ebenfalls kleiner wird (vgl. Kapitel 2.1). In den unteren Metallebenen ändert sich praktisch nur der Leiterquerschnitt - und somit nimmt der Eigenkapazitätsbelag stark ab. Der zusätzliche Effekt durch die abnehmende Dielektrizitätskonstante  $\varepsilon_r$  wurde schon in Kapitel 2.1 erwähnt. Für die Kopplung gegenüber dem Substrat bedeutet dies, dass diese mit kleiner werdenden Technologien verringert wird.

#### 2.1.2 Der Koppelkapazitätsbelag

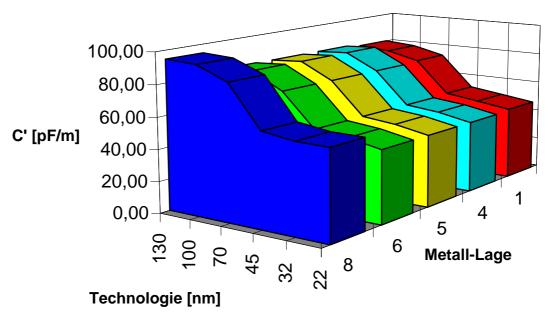

Die Koppelkapazität ist definiert als die Kapazität zwischen zwei Leitern. Entscheidend für deren Grösse ist die Höhe des Leiters (also die Fläche eines Leiters, die dem Nachbarleiter zugewandt ist) und der Abstand zwischen den Leitern. Bild 2.8 zeigt das Verhalten des Koppelkapazitätsbelages  $C_{34}'$  (Kopplung zwischen Leiter 3 und 4 im beschriebenen 5-Leiter-System) bei Kupferleitern in 5 ausgewählten Metallebenen. Deutlich lässt sich erkennen, dass sich der kapazitive

**Bild 2.8:** Koppelkapazitätsbelag der mittleren Leitung eines 5-Leitersystems

Kopplungseinfluss mit kleiner werdenden Technologien verringert und auf einen nahezu konstanten Wert zusteuert. In den Simulationen in Kapitel 5 ist dieser abnehmende Einfluss der Technologie deutlich erkennbar. Aufgrund der geometrischen Struktur der Leiter in den unterschiedlichen Metallebenen ist die Grösse des Koppelkapazitätsbelages unterschiedlich, das Verhalten über die verschiedenen Technologien ist jedoch identisch. Nach den Parametern der SIA Roadmap sind die kapazitiven Kopplungseffekte in den lokalen Verdrahtungsebenen 1 und 2 am geringsten und in den globalen Verdrahtungsebenen 7 und 8 am grössten. Aber auch in diesen Metallebenen zeigt sich der gleiche Verlauf über die Technologien und den damit erreichten konstanten Wert der Koppelkapazitäten bei kleineren Technologien. Die Effekte, die durch die Koppelkapazitäten hervorgerufen werden, schwächen sich somit in allen Metallebenen mit kleiner werdenden Technologien ab. Vergleicht man die Werte der Koppelkapazität mit denen der Eigenkapazität (Bild 2.2), so sind die der Koppelkapazität um den Faktor 4 bis 22

|                | Technologie |        |       |       |       |       |  |  |  |

|----------------|-------------|--------|-------|-------|-------|-------|--|--|--|

| Metallebene    | 130 nm      | 100 nm | 70 nm | 45 nm | 32 nm | 22 nm |  |  |  |

| 1              | 3,77        | 4,71   | 5,90  | 7,80  | 9,45  | 10,90 |  |  |  |

| 4              | 8,51        | 9,56   | 10,49 | 12,31 | 14,24 | 14,90 |  |  |  |

| 5              | 9,49        | 10,52  | 11,43 | 13,25 | 15,22 | 15,80 |  |  |  |

| <b>6</b> 12,04 |             | 12,97  | 13,78 | 15,74 | 17,95 | 18,21 |  |  |  |

| 8              | 15,18       | 15,14  | 16,49 | 18,21 | 20,82 | 22,07 |  |  |  |

je nach Metallebene grösser. In der 130nm Technologie ist der Kopplungsfaktor

**Tabelle 2.2:** Kapazitiver Kopplungsfaktor  $k = \frac{C_{koppel}}{C_{eigen}} = \frac{C_{34}}{C_{33}}$  der benachbarten Leitungen 3 und 4 in Abhängigkeit von Technologie und Metall-Lage

$k = \frac{C_{koppel}}{C_{eigen}}$  in der globalen Verdrahtungsebene 8 um den Faktor 5 grösser als in der lokalen Ebene 1. In der 22nm Technologie hingegen reduziert sich dieses Verhältnis von Ebene 8 zu Ebene 1 auf den Faktor 2. Deutlich ist jedoch der starke Anstieg des Kopplungsfaktors mit kleiner werdender Technologie zu erkennen. Es ist offensichtlich, dass nicht die kapazitive Kopplung gegenüber dem Substrat, sondern die Kapazität zwischen stromführenden Leitern in Zukunft von Bedeutung sein wird.

### 2.2 Der Induktivitätsbelag L'

Der Induktivitätsbelag ist bei gekoppelten Leitungen inzwischen ebenso wichtig wie die Parameter R' und C', wird jedoch in vielen Leitungsmodellen möglicherweise deshalb nicht berücksichtigt, weil seine Berechnung besonders bei dreidimensionalen Strukturen äusserst schwierig ist [2]. Der Indukivitätsbelag setzt sich aus der frequenzunabhängigen äusseren Induktivität  $L_a'$  und der frequenzabhängigen inneren Induktivität  $L_i'$  zusammen ( $L_{ges}' = L_a' + L_i'$ ).

Die äussere Induktivität  $L_a'$  wird von der Leitungsgeometrie und den magnetischen Eigenschaften der Leitung bestimmt. Die innere Induktivität  $L_i'$  rührt von den Magnetfeldern in den Leitern her und nimmt mit zunehmender Frequenz ab, da die Leiterquerschnitte mehr und mehr feldfrei werden. Die äussere Induktivität wird beschrieben durch das Feld, das durch die Fläche zwischen Hin- und Rückleiter hindurchtritt.

Der Zusammenhang zwischen magnetischer Feldenergie und Induktivität ist durch die Formel

$$2W'_{mag} = \sum_{k} \sum_{n} I_{k} I_{n} L'_{kn}$$

gegeben (vgl. [35]). Für eine Doppelleitung ergibt sich daher:

$$W = \frac{1}{2}L_1I_1^2 + MI_1I_2 + \frac{1}{2}L_2I_2^2$$

Bei stark verlustbehafteten Leitungsstrukturen spielt die induktive Kopplung eine nicht dominierende Rolle, hingegen führt bei gut leitenden Leitungen eine Vernachlässigung der Induktivität zu einem Fehler bei der Modellierung eines gekoppelten Leitungssystems [70]. Im Skin-Effekt Mode (vgl. Bild 2.2) gilt für den gesamten Induktivitätsbelag ohne Berücksichtigung von Randeffekten nach [35] folgende Näherungsformel (Abstand zum Rückleiter b, Leiterdurchmesser w, Eindringtiefe  $\delta$ ) für Rundleiter:

$$L' \approx \mu_0 \frac{b + \delta/2}{w}$$

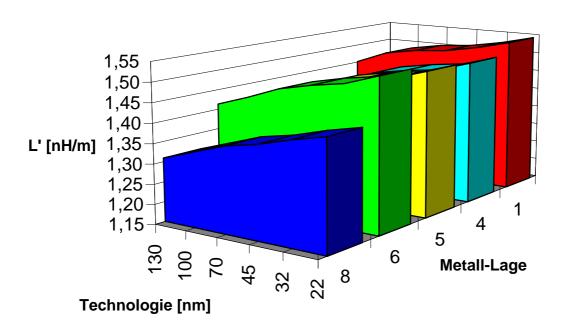

#### 2.2.1 Der Selbstinduktivitätsbelag

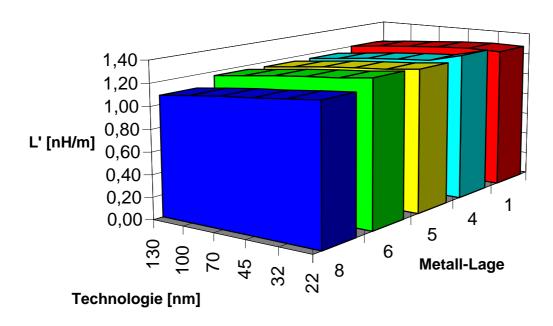

Bild 2.9 zeigt das Verhalten des gesamten Selbstinduktivitätsbelages  $L'_{ges}$  bei Kupferleitern in einer Ebene in 5 der 8 Metallebenen bei einer Substratleitfähigkeit von  $\sigma=10000S/m$ . In der globalen Verdrahtungsebene 8 besitzt die Selbstinduktivität den geringsten Wert gegenüber den anderen Metallebenen. Mit Verkleinerung der Technologie steigt der Induktivitätsbelag in jeder Metallebene gleichstark linear an. Eine Begründung dieses Verhaltens mit Hilfe analytischer Ausdrücke für rechteckige Leiter ist schwer: Einfacher ist es bei der Betrachtung von Rundleitern. Für einen Rundleiter gilt (a: Abstand zwischen Leitern bzw. Leiter und Substrat,  $r_0$ : Radius des Leiters):

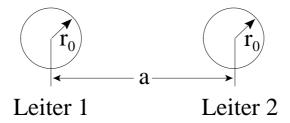

$$L' = \frac{\mu_0}{\pi} ln \frac{a - r_0}{r_0} \qquad \text{mit} \qquad a > r_0$$

Hier ist also das Verhältnis von Leiterradius und Abstand der Leiter bzw. zum Substrat für die Grösse des Induktivitätsbelages entscheidend (Bild 2.10). Diese einfache Näherungsformel gilt jedoch nur für Rundleiter mit vernachlässigbarem Querschnitt. Für die in dieser Arbeit untersuchten Rechteckleiter ist die mathematische Beschreibung nach [59] jedoch ungleich komplizierter, so dass nicht nur

**Bild 2.9:** Selbstinduktivitätsbelag der mittleren Leitung eines 5-Leitersystems

Bild 2.10: Anordnung für Näherungsformel des Induktivitätsbelages

das Verhältnis von Leiterradius und Abstand zum Substrat entscheidend ist. Für eine Komponente des Magnetfeldes bei Vernachlässigung von  $L_i$  gilt:

$$H_{z} = \frac{I}{2\pi ab} \left[ \frac{1}{2} \left( x + \frac{b}{2} \right) ln \frac{\left( y + \frac{a}{2} \right)^{2} + \left( x + \frac{b}{2} \right)^{2}}{\left( y - \frac{a}{2} \right)^{2} + \left( x + \frac{b}{2} \right)^{2}} \right.$$

$$- \frac{1}{2} \left( x - \frac{b}{2} \right) ln \frac{\left( y + \frac{a}{2} \right)^{2} + \left( x - \frac{b}{2} \right)^{2}}{\left( y - \frac{a}{2} \right)^{2} + \left( x - \frac{b}{2} \right)^{2}}$$

$$+ \left( y + \frac{a}{2} \right) \left( \arctan \frac{x + \frac{b}{2}}{y + \frac{a}{2}} - \arctan \frac{x - \frac{b}{2}}{y + \frac{a}{2}} \right)$$

$$- \left( y - \frac{a}{2} \right) \left( \arctan \frac{x + \frac{b}{2}}{y - \frac{a}{2}} - \arctan \frac{x - \frac{b}{2}}{y - \frac{a}{2}} \right) \right]$$

In ähnlicher Weise lässt sich  $H_y$  und  $H_x$  bestimmen.

Eine einfache Abschätzung des Induktivitätsverhaltens in Abhängigkeit von der Leitergeometrie ist bei einem Rechteckleiter demnach nicht ohne weiteres möglich und lässt sich daher meist nur mit Feldberechnungsprogrammen bestimmen.

#### 2.2.2 Der Gegeninduktivitätsbelag

Bild 2.11 zeigt das Verhalten des Gegeninduktivitätsbelages L' bei Kupferleitern in 5 ausgewählten Metallebenen. Es zeigt sich ein ähnliches Verhalten wie bei der Selbstinduktivität: Mit kleiner werdenden Technologien und damit verbundenen kleineren Strukturgrössen steigt auch der Wert der Gegeninduktivität linear an. Äquivalent zum Selbstinduktivitätsbelag ist bei der Grösse der Gegeninduktivität das Verhältnis von Leiterquerschnitt und Leiterabstand entscheidend (Bild 2.10).

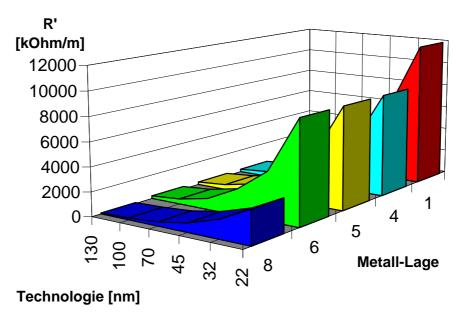

### 2.3 Der Widerstandsbelag R'

Kapazitäts- und Induktivitätsbelag scheinen trotz eines Anstieges mit kleiner werdenden Technologien unkritisch. Das grösste Problem in den Nanometertechnologien wird allerdings der Widerstandsbelag sein. Die ohmschen Verluste aufgrund der Längsströme durch Leiter inklusive Rückleiter bzw. auch Substrat werden durch den Widerstandsbelag R' repräsentiert. Da die Leitungsquerschnitte auf Chips sehr gering sind, sind die Widerstandsbeläge von Leitungen auf integrierten Digitalschaltungen ausserordentlich hoch. Mit der zunehmenden Miniaturisierung der Leiterquerschnitte in den künftigen Technologien wird der Widerstandsbelag nahezu exponentiell ansteigen. Geht man zusätzlich davon aus, dass

Bild 2.11: Gegeninduktivitätsbelag der mittleren Leitung eines 5-Leitersystems

die durchschnittliche Leitungslänge von globalen Verbindungsleitungen auf Chips sich bis zum Jahr 2014 nahezu verdoppeln wird, trägt der stark ansteigende Widerstandsbelag zusammen mit grossen Leitungslängen sowie den Kapazitätsbelegen zu einer ausserordentlich starken Erhöhung der Signallaufzeit bei. Mit steigender Frequenz ist es natürlich wünschenswert, eine minimale Verzögerung auf einer Leitung zu gewährleisten, da ansonsten eine fehlerfreie Übertragung des Digitalsignals unmöglich wird. Dem widersprechen aber die immer kleiner werdenden Strukturgrössen und Leiterquerschnitte. Um dem hohen Anstieg des Widerstandsbelages entgegenzuwirken, wird in letzter Zeit fast ausschliesslich Kupfer als Leitermaterial eingesetzt und hat Aluminium nahezu vollständig verdrängt. Kupfer besitzt einen spezifischen Leitwert von ca. 56 · 10<sup>6</sup> S/m, Aluminium dagegen nur einen fast halb so hohen Wert von lediglich 30 · 10<sup>6</sup> S/m. Dies bedeutet, dass der Widerstandsbelag durch die Verwendung von Kupfer als Leitermaterial fast um die Hälfte reduziert werden kann. Für die Übertragung eines Digitalsignals bedeutet dies wiederum, dass aufgrund einer geringeren Dämpfung bei gleicher Leitergeometrie und gleicher Leitungslänge ein Signal auf einem Kupferleiter mit ungefähr √3facher Signalfrequenz gegenüber eines Aluminiumleiters fehlerfrei auf einer Einzelleitung übertragen werden kann - bei parallelen Leitungen kann diese Frequenz allerdings aufgrund elektromagnetischer Kopplung nicht erreicht werden.

Bild 2.12 zeigt den Widerstandsbelag des mittleren Leiters  $R_3$  des verwendeten 5-Leitersystems (Bild 2.1) in Abhängigkeit der Technologien und in 5 ausgewählten Metallebenen. Die prozentual stärkste Zunahme des Widerstandsbelages tritt

**Bild 2.12:** Widerstandsbelag R' der mittleren Leitung eines 5-Leitersystems

in den Metallebenen für mittlere Leitungslängen (Metall-Lagen 3-6) auf. Während sich die Strukturgrössen beim Übergang von der 130nm Technologie in die 22nm Technologie um den Faktor 6 verringern, steigt der Widerstandsbelag in Metallebene 1 um das 40fache. In der Metallebene 8, in der globale, lange Verbindungsleitungen geführt werden, ist die Zunahme immerhin noch das 35fache gegenüber der heutigen 130nm Technologie. In der untersten Metallebene (Zunahme 33fach) werden kurze, lokale Verbindungsleitungen geführt, so dass eine sehr starke Erhöhung des Widerstandsbelages zwar zu einer grossen Verzögerung führt, die jedoch bei diesen kurzen Leitungen noch nicht sehr kritisch ist. Globale Verbindungsleitungen werden in den Metallebenen 7 und 8 in ihrem Querschnitt wesentlich grösser dimensioniert als die lokalen Leitungen in Metallebene 1 und 2 (siehe Bild 2.1). Dadurch ist der Querschnitt von Leitern in Metallebene 7 und 8 um vier bis fünf mal grösser als in Metallebene 1 bzw. 2. Damit reduziert sich der Widerstandsbelag um ca. den Faktor 4 gegenüber dem in Metallebene 1 bzw. 2. Dennoch erreichen die Widerstandsbeläge Werte im MΩ-Bereich. Der Widerstandsbelag vergrössert sich nicht nur quadratisch wie im Gleichstromfall  $(R = \frac{\rho}{4})$ , sondern in allen Metallebenen mit kleiner werdenden Technologien nahezu exponentiell: in Metallebene 1 und 2 von 355 k $\Omega$  auf fast 12 M $\Omega$  und in Metallebene 7 und 8 immerhin noch von 79 k $\Omega$  auf fast 3 M $\Omega$ . Für globale -

und damit lange - Leitungssysteme von mehr als 1 mm Leitungslänge ist dieser Anstieg dramatisch, da sich die Signallaufzeit drastisch erhöht.

Die Widerstandsbelagsmatrix R' ist bei niedrigen Frequenzen eine Diagonalmatrix, wobei die einzelnen Elemente gleich den Widerstandsbelägen der einzelnen Leitungen sind. Ab ca. 5 GHz sind die Nebendiagonalelemente jedoch nicht mehr vernachlässigbar [37].

Zusammenfassend wirkt sich von den Grössen die Änderung des Induktivitätsbelags am wenigsten auf das Signalverhalten in den zukünftigen Technologien aus. Verglichen mit dem Kapazitätsbelag und erst recht mit dem Widerstandsbelag ist die Veränderung der Induktivitätsbeläge rein linear und ändert nicht ihren Wert um Grössenordnungen wie bei den anderen Leitungsparametern.

# 3 Leitungssimulation im Zeitbereich

Zur Beschreibung des Signalverhalten auf Verbindungsleitungen ist grundsätzlich eine Simulation im Frequenz- oder im Zeitbereich möglich. Bei Simulationen im Frequenzbereich muss eine Transformation vom Zeit- in den Frequenzbereich und wieder zurück erfolgen, da die Resultate letztlich im Zeitbereich benötigt werden. Zwar können lineare zeitinvariante Systeme im Frequenzbereich wesentlich einfacher beschrieben werden als im Zeitbereich. Da die mit den Leitungen verbundenen aktiven Bauelemente in mikrolektronischen Schaltungen jedoch meist stark nichtlinear sind, ist eine Beschreibung im Frequenzbereich nur schwer möglich. In dieser Arbeit erfolgt daher die Beschreibung des Signalverhaltens vollständig im Zeitbereich.

Mathematisch beschreiben lässt sich eine Anordnung durch Ansetzen der Maxwellschen Gleichungen. Allerdings gilt es dann ein meist sehr kompliziertes Randwertproblem zu lösen, wobei analytische Lösungen nur für Spezialfälle existieren. Numerisch ist eine Lösung möglich, wenn insgesamt 4 Dimensionen (3 räumliche Dimensionen und die Zeit) berücksichtigt werden, allerdings entsteht so ein Gleichungssystem von solcher Grösse, dass es in vertretbarer Zeit nicht lösbar ist. Weniger zeitaufwendige Simulationen erreicht man durch Reduzierung der vier auf weniger Dimensionen.

### 3.1 Beschreibungsarten im Zeitbereich

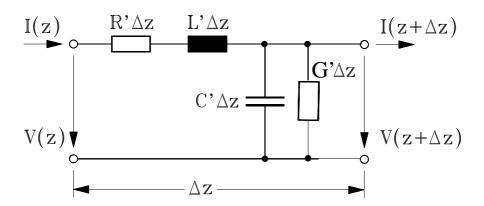

#### 3.1.1 Diskretes Netzwerkmodell

Durch Reduzierung der 4 Dimensionen auf eine Dimension wird der Zeitaufwand für die Simulation deutlich geringer. Dazu wird ein Modell aufgestellt, das nur durch seine Topologie und die Zeit beschrieben wird, also ein Netzwerkmodell. Die räumlichen Dimensionen werden nur noch durch die Angabe der Knoten zwischen den Bauelementen, also durch den Zusammenhang der verschiedenen Elemente des Netzwerkes, und alle anderen Eigenschaften der Leitung durch ein konzentriertes Netzwerksegment aus Widerstand R, Leitwert G, Kapazität C und Induktivität L, erfasst (Bild 3.1). Durch diese starke Vereinfachung kann die so

**Bild 3.1:** Leitungsmodell durch RLCG-Netzwerk

entstandene Schaltung sehr einfach mit Hilfe nahezu aller bekannter Netzwerkanalyseprogramme simuliert werden. Allerdings wird dieser Vorteil dadurch erkauft, dass aufgrund der Dimensionsreduzierung ein grosser Informationsverlust

bezüglich des tatsächlichen physikalischen Leitungssystems entsteht, so dass das

erzeugte Netzwerkmodell die Realität nur noch sehr vereinfacht beschreibt. Während die exakte vierdimensionale Beschreibung auf partielle Differentialgleichungen führt, erfolgt die mathematische Beschreibung des eindimensionalen Netzwerkmodells mit diskreten Elementen durch gewöhnliche Differentialgleichungen. Es ist jedoch a priori unmöglich mit Hilfe gewöhnlicher Differentialgleichungen Effekte zu beschreiben, die typisch für Wellenausbreitung sind. Diese

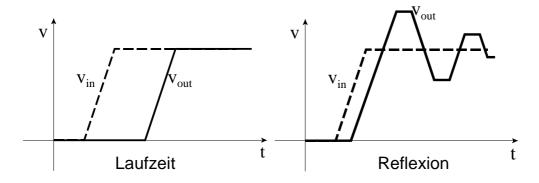

typischen Effekte wie Laufzeit und Reflexion sind wichtige Eigenschaften, die

meistens nicht zu vernachlässigen sind (Bild 3.2). Die Beschreibung erfolgt voll-

**Bild 3.2:** Leitungseffekte Laufzeit und Reflexion

ständig quasistationär, d.h. das an einem Netzwerkknoten stattfindende Ereignis ist zeitgleich an allen anderen Knoten sofort wirksam, also ohne jede Zeitverzögerung. Eine sog. Totzeit existiert in Netzwerken nicht. Dies ist jedoch, wie leicht

ersichtlich, unphysikalisch, denn ein Signal breitet sich auf einer endlichen Leitung zwar mit 30-50 Prozent der Lichtgeschwindigkeit aus, dennoch wäre es ein nicht-kausales System, wenn das Signal zum gleichen Zeitpunkt am Anfang und am Ende der Leitung abgreifbar wäre. Man kann die oben beschriebenen Effekte ein wenig verbessern, wenn das Netzwerkmodell der Leitung durch sehr viele, kaskadierte Netzwerkelemente modelliert wird. Dadurch steigt jedoch auch die Simulationsdauer sehr stark an.

#### 3.1.2 Verteilte Elemente

Reduziert man die Dimensionen der Schaltungsbeschreibung nicht auf eine, sondern nur auf zwei Dimensionen (Zeit, Topologie und die Längendimension der Leitung), vereinfachen sich die das System beschreibenden Differentialgleichungen immer noch erheblich. Quer zur Ausbreitungsrichtung erfolgt die Beschreibung weiterhin quasistationär, aber längs zur Ausbreitungsrichtung schnellveränderlich. Der Vorteil dieses Modells ist, dass bei der Simulation keine numerische Integration notwendig ist, wie sie z.B. bei der Leitungsmodellierung mit RLCG-Elementen unumgänglich ist. Das in dieser Arbeit und im Simulator ELDO [33] verwendete Leitungsmodell [64] basiert auf dem beschriebenen Algorithmus. Detaillierte Beschreibungen sind in [35] und [74] zu finden.

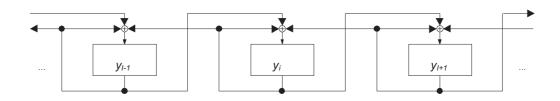

### 3.2 Wellenausbreitung auf Mehrfachleitungen

Die in dieser Arbeit behandelten Leitungssysteme werden verstanden als eine beliebige Anzahl von Einzelleitungen, die elektrisch und magnetisch miteinander verkoppelt sind und sich in einem Medium befinden, das in Wellenausbreitungsrichtung, also in Längsrichtung der Leitungen, hinsichtlich der elektromagnetischen und geometrischen Eigenschaften mindestens stückweise homogen ist. Beschrieben wird die Wellenausbreitung auf Leitungssystemen nach [35] durch ein verkoppeltes System partieller Differentialgleichungen.

$$\frac{\partial \underline{V}}{\partial z} = -\left(R' + L'\frac{\partial}{\partial t}\right)\underline{I}$$

$$\frac{\partial \underline{I}}{\partial z} = -\left(G' + C'\frac{\partial}{\partial t}\right)\underline{V}$$

Bei R' (ohmsche Verluste aufgrund der Längsströme durch die Leiter pro Längeneinheit), L' (Magnetfeld mit magnetischer Kopplung pro Längeneinheit), C'

(elektrisches Feld mit elektrischer Kopplung pro Längeneinheit) und G' (Leitwerte pro Längeneinheit durch Querströme) handelt es sich um quadratische Matrizen der Dimension  $n \times n$ , und bei den unterstrichenen Grössen  $\underline{V}$  (elektrische Potentiale aller n Leiter des Leitungssystems gegenüber dem gemeinsamen Rückleiter) und  $\underline{I}$  (elektrische Ströme aller n Leiter) um Spaltenmatrizen, also Matrizen der Dimension  $n \times 1$ . n steht hierbei für die Anzahl der Leitungen eines Leitungssystems exklusive des gemeinsamen Rückleiters. Wie in Kapitel 2 erwähnt wurde, kann die Leitwertmatrix meist vernachlässigt werden, da die Leiter i.a. gegeneinander hinreichend gut isoliert sind.

Durch Differentiation und Substitution erhält man unter der erwähnten Vernachlässigung von G':

$$\frac{\partial^2 \underline{V}}{\partial z^2} = L'C' \frac{\partial^2 \underline{V}}{\partial t^2} + R'C' \frac{\partial \underline{V}}{\partial t}$$

Durch Lösen dieses partiellen Differentialgleichungssystems lässt sich die Wellenausbreitung auf Leitungssystemen berechnen. Für verlustbehaftete Leitungssysteme ( $R' \neq 0$ ) ist dies jedoch meist nur numerisch möglich. Einfacher ist es, das Leitungssystem erst verlustlos anzunehmen, die Lösung zu berechnen und anschliessend die Leitungsverluste zu berücksichtigen. Dazu wird die Leitung zunächst in kurze Leitungsstücke gleicher Länge zerlegt, so dass die Laufzeit durch diese Segmente gleich gross ist. Zwischen die einzelnen Segmente wird dann jeweils ein ohmscher Widerstand geschaltet, so dass durch diese Anordnung die Leitungsverluste berücksichtigt werden können (Details sind in [35] zu finden).

### 3.3 Leitungssimulation

In dieser Arbeit wurde der Schaltungssimulator ELDO mit dem am Laboratorium für Informationstechnologie entwickelten Makromodell LOSSYWIRE [40] zur Simulation von verlustbehafteten Leitungssystemen mit verteilten Elementen verwendet. ELDO basiert auf dem Analyseprogramm für elektronische Schaltungen SPICE [47]. Eine detaillierte Beschreibung der Funktionsweise des Simulationsmodells LOSSYWIRE ist in [64] und [65] erläutert. Die Vorteile dieses Verfahrens gegenüber einer Modellierung mit diskreten RLC-Netzwerken wurden in Kapitel 3.1.2 erläutert.

Physikalisch realistischer ist die Simulation mit verteilten Elementen, jedoch mathematisch schwieriger als der Aufbau eines RLC-Netzwerkes. Eine Simulation mit verteilten Elementen ist jedoch deutlich schneller. Oft wird bei Verwendung des diskreten Netzwerkmodells auf die Anwendung des Induktivitätsbelages verzichtet (RC-Netzwerk), damit einerseits das Problem der Extraktion der Induktivitätsbeläge entfällt und andererseits die Simulation beschleunigt wird.

Inwieweit diese Vernachlässigung zu Ungenauigkeiten im Simulationsverhalten führt, zeigt dieses Kapitel im Vergleich der drei möglichen Verfahren (RLC-, RC-, LOSSYWIRE-Simulation). Dabei wird insbesondere gezeigt, zu welchen Unterschieden die Anwendung dieser Verfahren auf Geometrien der Nanometer-Technologien, also mit stark verlustbehafteten Leitungen, führen.

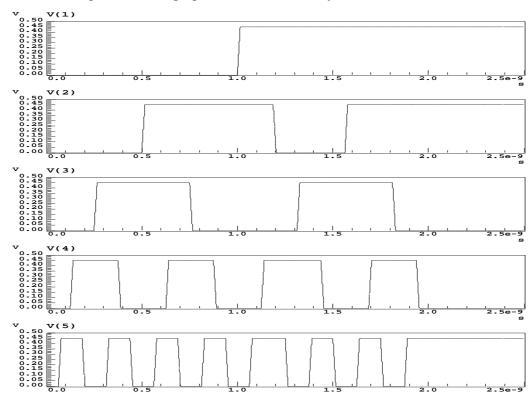

#### 3.3.1 Vergleich Lossywire, RLC und RC-Simulation

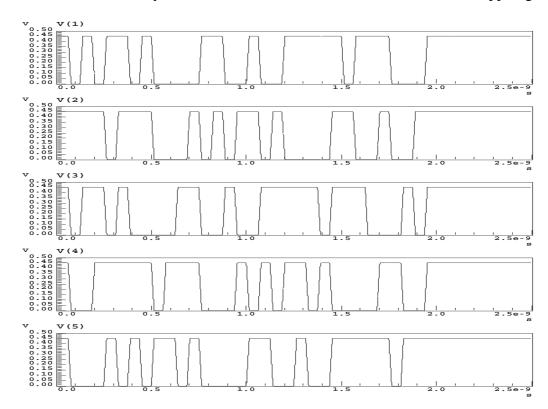

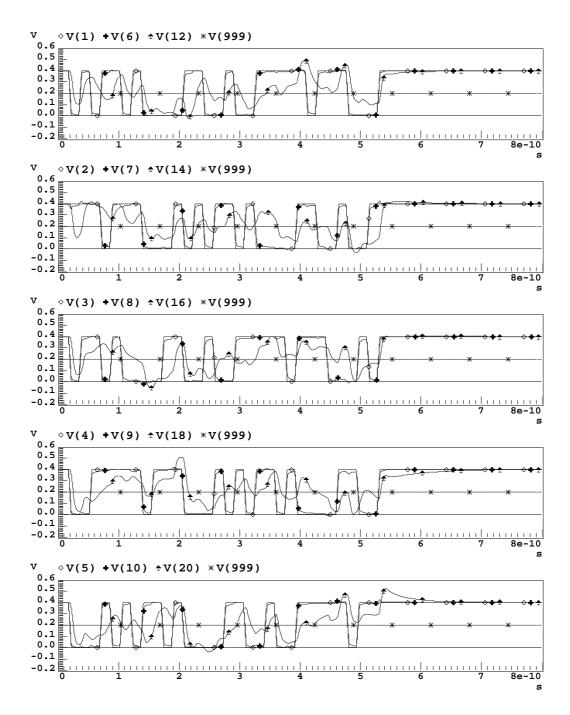

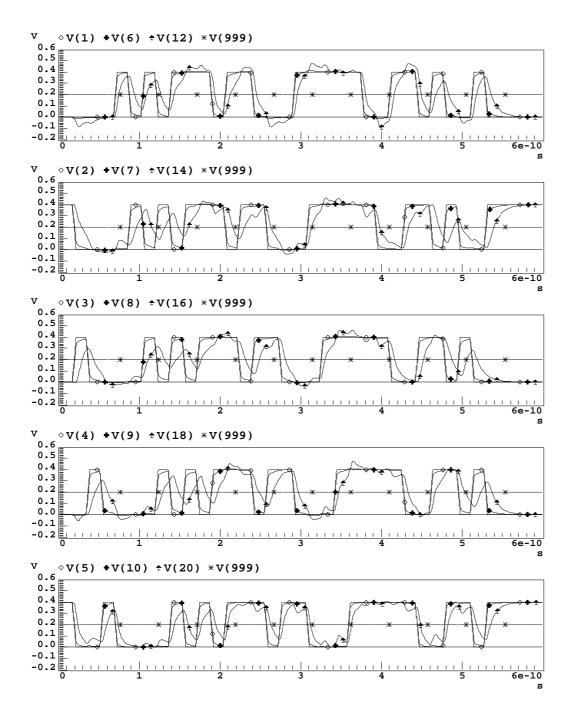

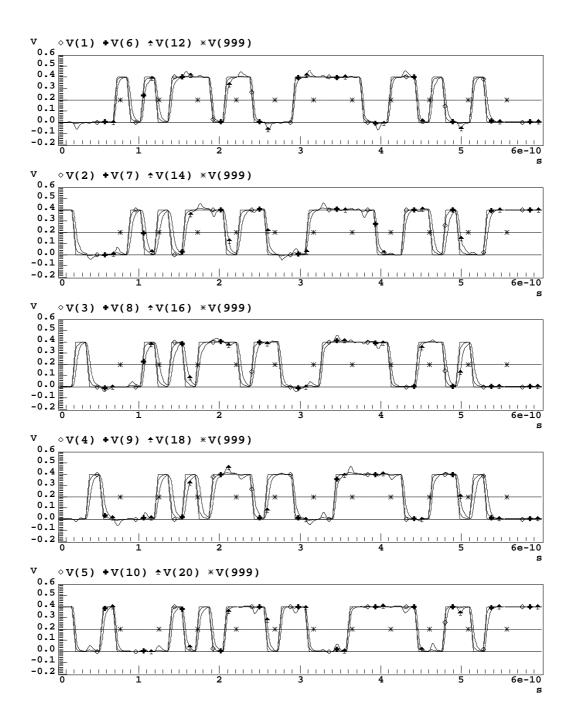

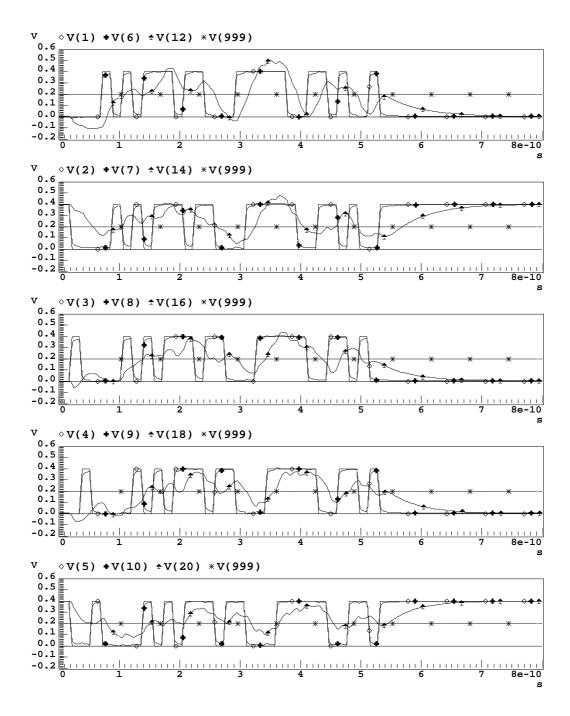

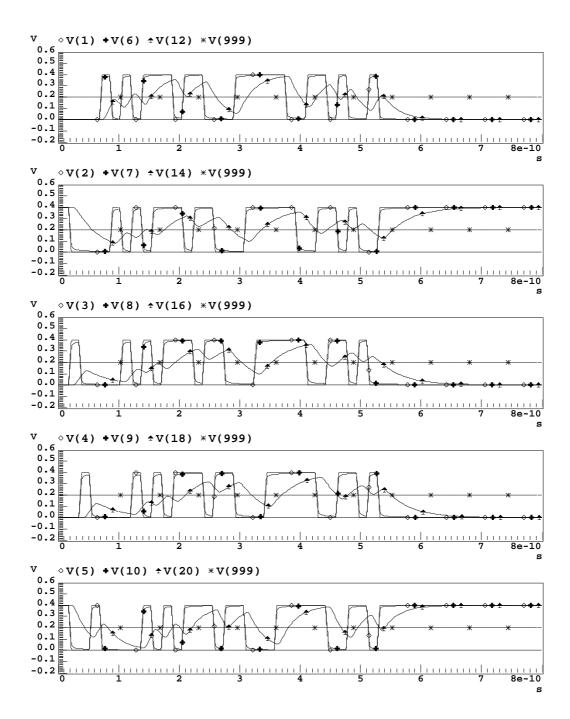

Zum Vergleich der drei Simulationsverfahren wird ein paralleles Leitersystem aus fünf Kupferleitern simuliert. Dabei wird die Chip-Geometrie aus Kapitel 2 zugrundegelegt. Als Leitergeometrie werden die Abmessungen für globale Verbindungsleitungen in Metallebene 8 verwendet. Die Leitungslänge beträgt  $500\mu m$  bei einer Substratleitfähigkeit von  $\sigma = 10000\frac{S}{m}$ . Das Leitersystem wird mit einem Testmuster eines 5 Bit-LFSR bei der maximalen Taktfrequenz, die laut SIA Roadmap bei der jeweiligen Technologie erwartet wird, beaufschlagt.

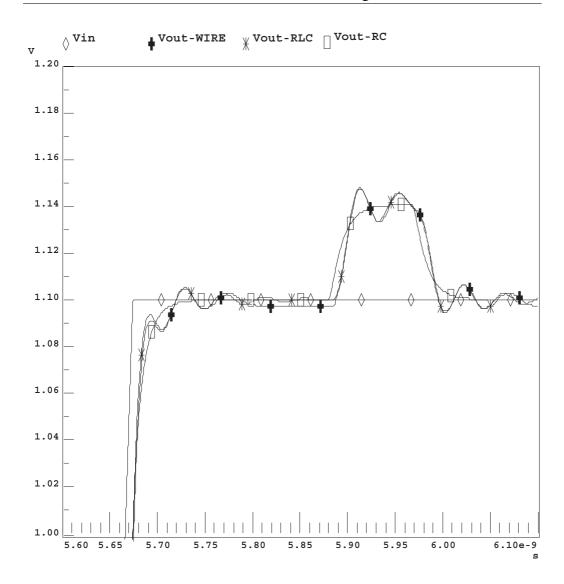

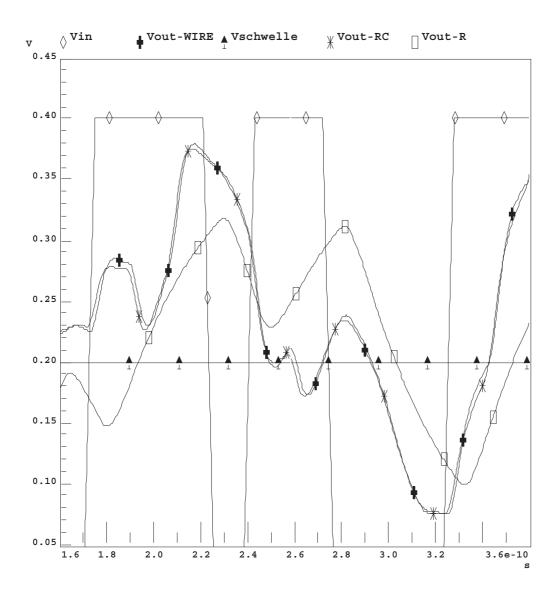

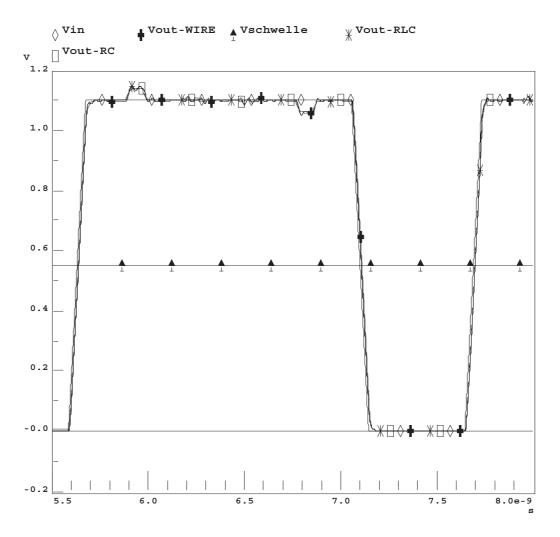

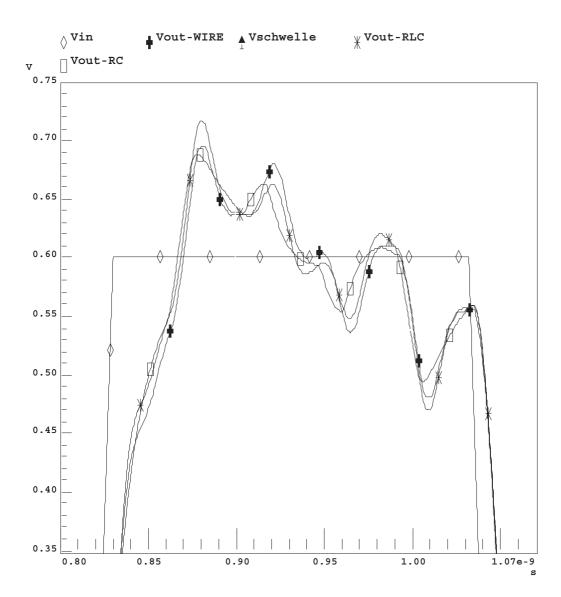

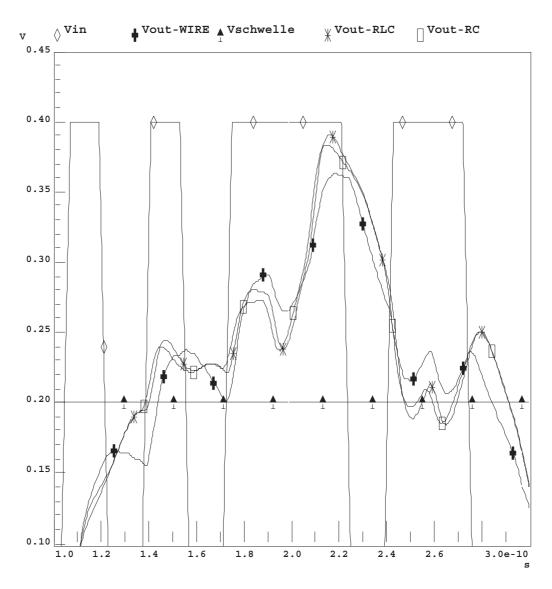

Bild A.1 im Anhang zeigt einen Vergleich der drei Simulationsarten bei einem Impulssignal an einem 5 Bit breiten Leitungssystem der Länge  $500\mu m$  in der 130nm Technologie. Dargestellt ist das Eingangssignal Vin der mittleren Leitung und das jeweilige Ausgangssignal Vout-WIRE der Lossywire Simulation sowie Vout-RLC der RLC und Vout-RC der RC Simulation mit jeweils 20 Segmenten. Zunächst ist nur erkennbar, dass in dieser Technologie das Signal nahezu ungestört zum Ausgang propagiert wird.

In starker Vergrösserung zeigen sich jedoch grosse Unterschiede zwischen den einzelnen Simulationsarten (Bild 3.3). Während sich das Ausgangssignal Vout-WIRE der Lossywire und Vout-RLC der RLC Simulation nahezu nicht unterscheiden (es ist lediglich in manchen Überschwingungen ein geringer Unterschied erkennbar), so zeigt sich, dass eine Simulation ohne Berücksichtigung der Induktivität lediglich mit RC Elementen (Vout-RC) zu einem sich stark unterscheidenden Signal führt. In der Simulation mit reinen ohmschen-kapazitiven Elementen wird das Schwingungsverhalten des Signales nicht korrekt erfasst. Der grundsätzliche analoge Signalverlauf ist zwar gegeben, aber das simulierte Signal ist wie eine Mittelwertbildung der genauen Simulation mit Lossywire oder RLC Elementen. Betrachtet man den Signalverlauf allerdings bezüglich des digitalen Schaltverhaltens, so wird das erwähnte Schwingungsverhalten uninteressant. Das digitale Schaltverhalten wird in allen drei Simulationsverfahren korrekt wiedergegeben. Das analoge Signalverhalten bei einer RC-Modellierung wird aufgrund des sehr hohen Widerstandsbelages bei kleineren Technologien im Vergleich mit der 130nm Technologie zwar weiterhin nicht korrekt wiedergegeben, für das digitale Schaltungsverhalten ist dies jedoch uninteressant. Alle drei Simulationsarten gleichen sich in ihrem analogen Signalverlauf an. Bild 3.4 zeigt

**Bild 3.3:** Vergleich: Lossywire, RLC und RC Simulation bei 130nm Technologie (Ausschnitt)

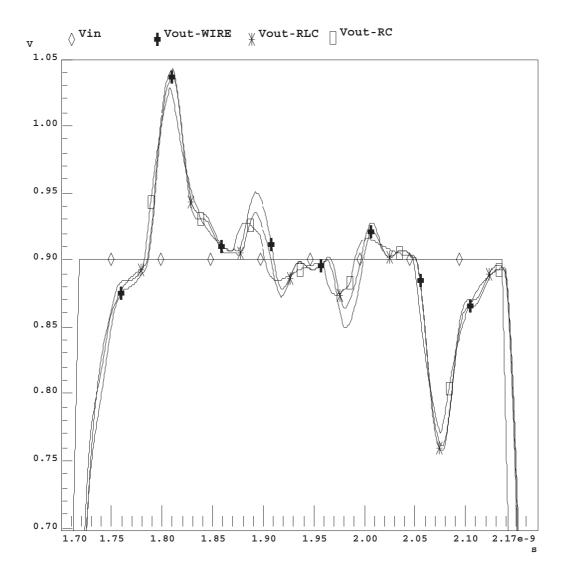

den Vergleich der Simulationsarten bei der 70nm Technologie eines ebenfalls 5 Bit breiten Leitungssystems bei gleicher Leitungslänge von  $500\mu m$ . Vin kennzeichnet wie zuvor das Eingangssignal der mittleren Leitung, Vout-WIRE das der Lossywire Simulation sowie Vout-RLC der RLC und Vout-RC der RC Simulation. Die Simulationsvergleiche der 45nm und 22nm Technologie sind in Anhang A zu finden.

**Bild 3.4:** Vergleich: Lossywire, RLC und RC Simulation bei 70nm Technologie (Ausschnitt)

In dieser Arbeit soll nicht gezeigt werden, dass die eine oder andere Simulationsbzw. Modellierungstechnik besser oder schlechter ist, da dies oft eine persönliche Entscheidung [103] ist. Da jedoch die Simulation mit Lossywire bei den hier untersuchten Leitungssystemen wesentlich schneller arbeitet und ausserdem die Laufzeit im Gegensatz zum RLC-Modell berücksichtigt wird, wurden alle Simulationen in dieser Arbeit mit diesem Algorithmus bzw. dem Programm ELDO mit dem Makromodell LOSSYWIRE 3.1.2 durchgeführt.

#### 3.3.2 Induktivitäten in den Nanometer-Technologien

Da die Taktfrequenz von mikroelektronischen Schaltungen in den Nanometertechnologien auf mehrere Gigahertz ansteigt und sich die Komplexität der Leitungssysteme erhöht, ist auch das genaue Modellieren hochfrequenter elektromagnetischer Eigenschaften wie z.B. induktive Kopplung wichtig [31], [39]. Die Ausbreitung der digitalen und analogen Signale wird durch die induktiven Effekte der Leitungen beeinflusst und die Signalintegrität durch induktive Kopplung verschlechtert. Selbstinduktivität von Leitungen, sowie Gegeninduktivität zwischen Leitungen werden in den kommenden Jahren von besonderem Interesse sein. Dabei ist die grösste Herausforderung, die parasitären Eigenschaften von komplizierten Leitungsstrukturen vorauszusagen.

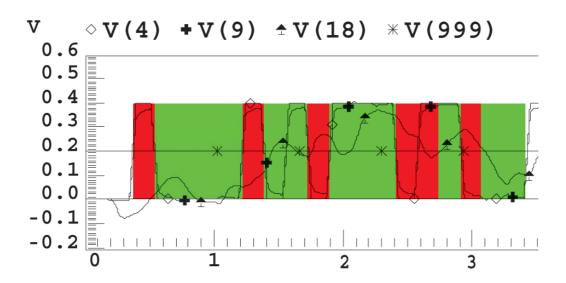

Betrachtet man die Ergebnisse aus Kapitel 3.3.1, so stellt sich die Frage:

"Wie wichtig ist die Berücksichtigung induktiven Koppelverhaltens in den Nanometer-Technologien?".

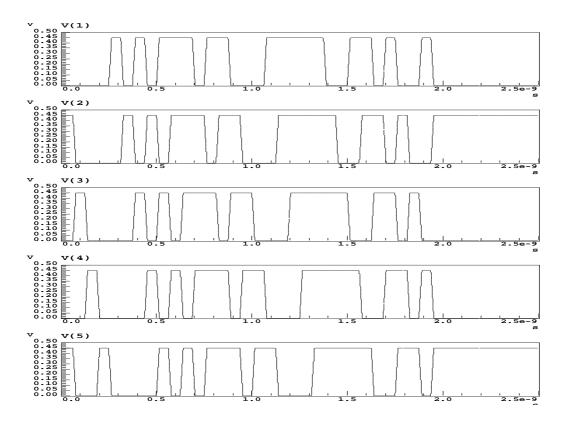

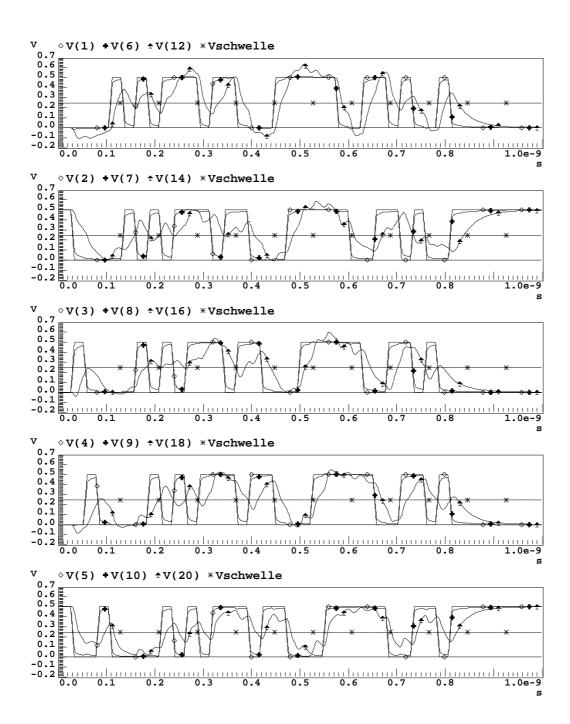

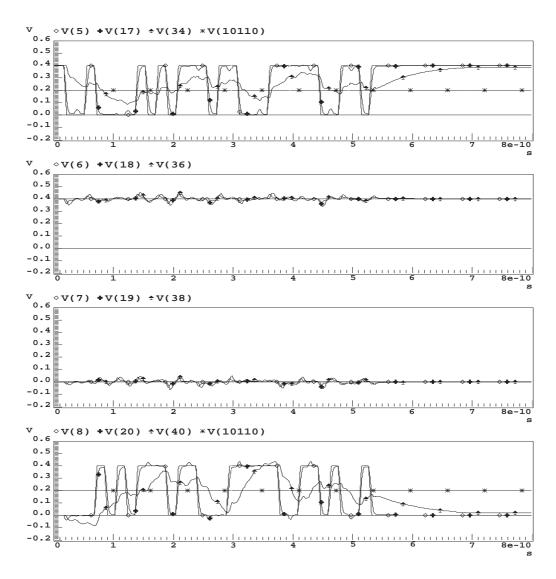

Zur Klärung dieser Frage wurde mit der Lossywire Simulation das obige 5 Bit breite Leitungssystem bei einer Leitungslänge von  $500\mu m$  einmal mit allen Leitungsparametern, dann nur mit kapazitiver, und schliesslich ohne induktive und kapazitive Kopplung, simuliert. Die Selbstinduktivitäten und Eigenkapazitäten werden selbstverständlich berücksichtigt. Bild 3.5 zeigt die unterschiedlichen Ergebnisse. Dabei stellt Vin das ideale Eingangssignal, Vout-WIRE das Ausgangssignal mit allen Leitungsparametern, Vout-RC das Ausgangssignal ohne induktive Kopplung und Vout-RC ohne C und ohne C

Sofort einzusehen ist, dass eine Simulation allein mit ohmschen Parametern keinerlei Kopplungseffekte wiedergibt und damit zu keinerlei Überschwingen führt, und daher auch für eine Simulation des genauen analogen Signalverhaltens unbrauchbar ist. Die Simulationsergebnisse ohne induktive Kopplung weichen analog betrachtet stark von denen mit mit vollständigen Parametern ab, bei digitaler Betrachtungsweise allerdings ist diese Abweichung unerheblich. Das analoge Schwingen des Signals wird jedoch nur bei der Simulation, die alle

**Bild 3.5:** Vergleich Lossywire Simulation mit allen Parametern, nur mit kapazitiver Kopplung und ohne Kopplung bei 130nm Technologie (Ausschnitt)

Leitungsparameter berücksichtigt, fehlerlos erfasst.

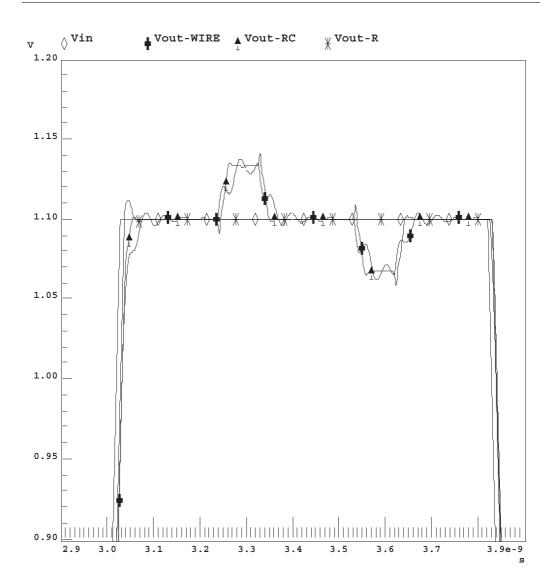

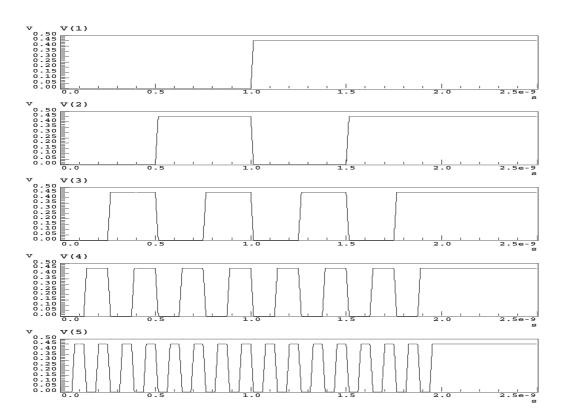

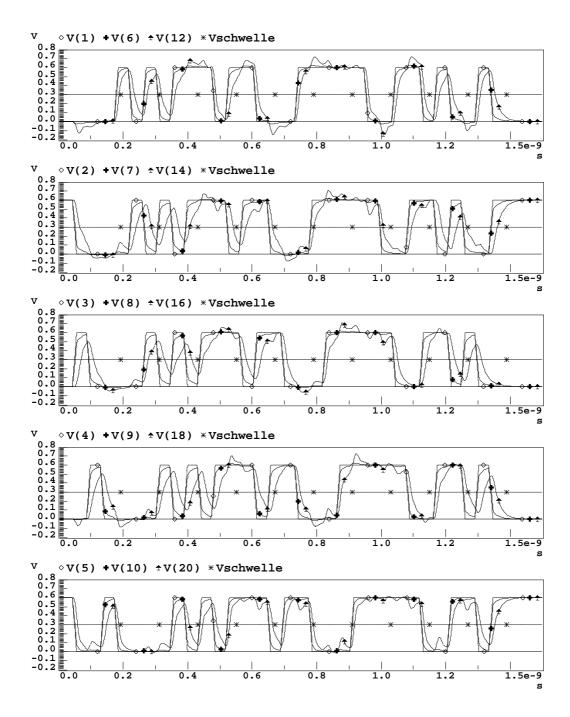

Was passiert nun aber, wenn die Leitungsgeometrien wesentlich kleiner, also verlustbehafteter, werden? Sind die Induktivitäten dann u.U. vernachlässigbar? Wie in Bild 3.5 (130nm Technologie) zeigt in Bild 3.6 (22nm Technologie) *Vin* das ideale Eingangssignal am Anfang der Leitung, *Vout-WIRE* das Ausgangssignal mit allen Leitungsparametern, *Vout-RC* das Ausgangssignal ohne induktive

**Bild 3.6:** Vergleich Lossywiresimulation mit allen Parametern, nur mit kapazitiver Kopplung und ohne Kopplung bei 22nm Technologie (Ausschnitt)

Kopplung und Vout-R das Ausgangssignal ohne C und ohne L.

Erneut ist sofort ersichtlich, dass eine Simulation ohne Koppelparameter nicht zu einem korrekten Ergebnis führt. Aber Bild 3.6 zeigt weiterhin ein nicht erwartetes Ergebnis: Die Simulation mit allen Parametern deckt sich mit der Simulation ohne induktive Kopplung und es ist kein nennenswerter Unterschied des Signalverlaufes mehr festzustellen. Dies wurde auch in weiteren Simulationen bestätigt. In den zukünftigen sehr kleinen Technologien mit sehr kleinen Leitergeometrien und da-

35

mit sehr stark verlustbehafteten Leitungssystemen kann also bei stark leitendem Substrat auf die Berücksichtigung der Gegeninduktivität verzichtet werden, da das Magnetfeld nicht in das Substrat eindringt. Wichtig allerdings wird die induktive Kopplung bei Leitungsmaterialien mit niedrigem Widerstandsbelag. Die hier simulierte Leitungslänge von  $500\mu m$  ist relativ kurz, aber wie schon erwähnt, können Signale bei der verwendeten Geometrie nicht fehlerfrei über längere Leitungssysteme in diesen kleinen Technologien übertragen werden. Insofern ist die gewählte Leitungslänge durchaus als charakteristisch für diese Technologien anzusehen. Keinesfalls jedoch darf die kapazitive Kopplung vernachlässigt werden - die Kopplung wird auch in zukünftigen Leitungssystemen eine äusserst wichtige Rolle spielen. Besitzt man die Möglichkeit ohne grossen Rechenaufwand alle Leitungsparameter, insbesondere die Induktivitäten, zu extrahieren, so sollte dies auch in Zukunft auf jeden Fall getan werden, denn nur so kann sichergestellt werden, dass das Verhalten einer Leitung auch korrekt erfasst werden kann. In dieser Arbeit wurden daher, wie schon erwähnt, alle Simulationen mit den vollbesetzten Leitungsparametermatrizen R', L' und C' durchgeführt. Auf Berücksichtigung der Leitwertmatrix G' wurde in dieser Arbeit verzichtet, da diese Parameter in den hier durchgeführten Untersuchungen zu vernachlässigen sind (Kapitel 2).

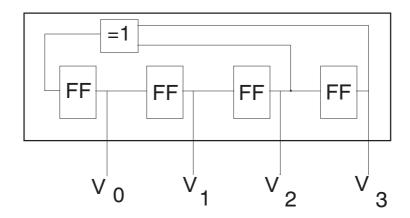

# 4 Testmustergeneratoren

Auch bei der sorgfältigsten Herstellung integrierter Schaltungen treten durch Verunreinigungen, Temperaturschwankungen, mechanische Störungen und andere Einflüsse Defekte auf. Aus diesem Grund muss eine Schaltung nach der Fertigung getestet werden, um einen eventuellen Fehler nachweisen zu können. Ziel dabei ist es, produktionsbedingt fehlerhafte Schaltungen von der fehlerfreien Schaltung zu unterscheiden.

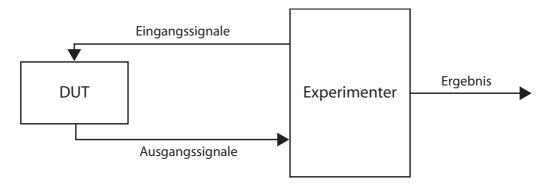

Das grundlegende Prinzip des Testens wird in der Arbeit von Moore [71] erläutert. Wie in Bild 4.1 dargestellt, wird ein Tester oder Experimenter definiert, der Eingangstestmuster an die zu testende Schaltung (DUT) anlegt und die Testantworten des DUT wieder abgreift. Diese Ausgangsmuster werden dann im Experimenter mit den Antworten eines Golden Device (der fehlerfreien Schaltung) verglichen. Weichen die beiden Antworten voneinander ab, so ist die getestete Schaltung fehlerhaft. Befindet sich der Experimenter ausserhalb des Chips, so spricht man von einem externen Tester (ATE). Ein Experimenter, der auf einem Chip integriert ist, wird als Selbsttest (BIST) bezeichnet.

**Bild 4.1:** Prinzipieller Aufbau eines Tests

Bei den in Zukunft zu erwartenden und in dieser Arbeit untersuchten hohen Taktraten (z.B. 3,4 GHz beim Pentium 4E) tritt in jedem Fall das Kopplungs- und das Delay-Problem auf Verbindungsleitungen auf. Dies und die hohen Personalkosten für externe Tests sind nach Rodgers [83] auch mit der Grund, warum in naher Zukunft Chips nur noch mit Selbsttest getestet werden können. Daher wird

in dieser Arbeit nur der Selbsttest (BIST) untersucht. Passive Testhilfen wie z.B. der Prüfbus, werden in [11] und [16] behandelt und in dieser Arbeit nicht weiter betrachtet.

Wesentliche Komponenten von BIST sind die Generatoren zur Erzeugung von Testmustern. Daher werden in dieser Arbeit diese Testmustergeneratoren bezüglich ihrer Eignung für verschiedene Technologien (vgl. SIA-Roadmap [7]) untersucht, da diese eine bedeutende Rolle beim Selbsttest spielen. In der Arbeit von Jorczyk [53] wurden Untersuchungen für entwickelte Selbsttestschaltungen für den GHz-Bereich durchgeführt.

Testmustergeneratoren sind Schaltungen, die zumeist aus Registern aufgebaut sind und sich mit auf dem Chip befinden. Durch eine geeignete Initialisierung werden diese Schaltungen in die Lage versetzt, Testmuster für eine zu testende Schaltung zu generieren. Die Testmustergeneratoren erzeugen pseudozufällige Bitfolgen von 0 und 1, die an die zu testende Schaltung angelegt werden. Die Ausgangsmuster, die am Ende der zu testenden Schaltung beobachtet werden (Testantwort), können dann zur Analyse der Schaltung verwendet werden. Dazu wird in einem Auswerter durch Verwendung der gleichen Teststimuli die Testantwort der integrierten Schaltung mit der aus einer Simulation der Netzliste erhaltenen Testantwort verglichen. Weichen diese beiden Muster in einem oder mehreren Bits voneinander ab, so liegt ein Fehler in der getesteten Schaltung vor.

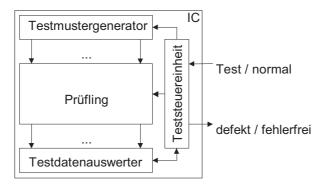

Einfacher und schneller ist es, wenn die zu testende Schaltung selbst, nachdem sie durch die Muster eines Testmustergenerators getestet wurde, durch das Setzen eines Flags meldet, ob sie fehlerhaft ist. Dies kann z.B. durch einen sog. BIST (Built-In Self-Test) erfolgen. Dazu wird die Schaltung durch einen Testdatenauswerter (TDA), eine Teststeuereinheit (TSE) und einen Testmustergenerator (z.B. rückgekoppeltes Schieberegister) erweitert. Bild 4.2 zeigt den prinzipiellen Aufbau einer Selbsttestschaltung in einer integrierten Schaltung.

**Bild 4.2:** Prinzipieller Aufbau einer Selbsttestschaltung

Dieser Test wird meist durch zwei Signale gesteuert (Einstellung des Testmodus und anstossen durch ein externes Bit) und generiert dann Testmuster direkt in der integrierten Schaltung. Ein Statusbit zeigt am Ende an, ob der interne Test erfolgreich verlaufen ist (vgl. auch Bild 4.2). Der grosse Vorteil des Selbsttests auf einem IC ist, dass keine externen Muster langsam und kompliziert an den Fehlerort herangebracht und propagiert werden müssen. Deshalb kann man pro Zeiteinheit eine viel grössere Anzahl von Testmustern erzeugen.

Dabei liefert der Testmustergenerator das Testmuster mit der die Schaltung getestet werden soll, die Teststeuereinheit koordiniert den Test und der Testdatenauswerter wertet die Testantworten aus. Auch ein Vergleich mit einer im lokalen ROM festgelegten sog. Signatur wird eingesetzt.

Übersichten über Möglichkeiten des Tests von mikroelektronischen Schaltungen sind vielfach in der Literatur veröffentlicht und können z.B. unter [1], [11], [28] sowie in [106] nachgelesen werden.

In den nachfolgenden Abschnitten werden zum späteren Verständnis die in dieser Arbeit untersuchten Testmustergeneratoren erläutert und beispielhaft ein Ausgangstestmuster bei einer bestimmten Initialisierung<sup>1</sup> gezeigt.

### 4.1 Zähler für den erschöpfenden Test

Ein digitales kombinatorisches Schaltnetz mit n Eingängen testet man erschöpfend (exhaustiv), indem man alle möglichen  $2^n$  Testmuster anlegt. Bei diesem Test hat man die Garantie, dass alle detektierbaren Fehler, die kein sequentielles Verhalten produzieren<sup>2</sup>, entdeckt werden. Ein solcher Test dauert jedoch je nach Anzahl der Eingänge und der Taktrate sehr lange, bei heutigen integrierten Schaltungen mit z.B. nur 64 Eingängen würde ein vollständiger Test bei einer fiktiv angenommenen Testzeit je Testmuster von nur 1ns über 584 Jahre dauern<sup>3</sup>. Indem man den vollständigen Test beschränkt, verkürzt er sich signifikant. Man nennt einen solchen Test einen pseudovollständigen (pseudoexhaustiv) Test. Die Beschränkung der Testmuster erreicht man durch verschiedene Formen der Partitionierung, also der Unterteilung der Schaltung in Teilschaltungen, die dann alle vollständig getestet werden können. Die Schaltung läßt sich logisch, z.B. in

<sup>&</sup>lt;sup>1</sup> Ein und derselbe Testmustergenerator erzeugt unterschiedliche Bit-Musterfolgen durch eine unterschiedliche Initialisierung

$<sup>^2</sup>$  bei sequentiellen Schaltwerken ist ein vollständiger Test im allgemeinen nicht anwendbar, da die m inneren Zustände mit berücksichtigt werden müssen und sich dadurch die Testzeit erhöht:  $2^{n+m}$

<sup>&</sup>lt;sup>3</sup> 2<sup>64</sup> Testmuster bei 1ns Testzeit/Muster = 18.446.744.073 Sekunden

Steuer- und Dateneingänge, oder physikalisch unterteilen. Die Ein- und Ausgänge der Unterschaltungen müssen kontrollierbar und observierbar sein. Weitere Details finden sich in [1].

#### 4.1.1 Binärzähler

Binärzähler können für einen erschöpfenden Test verwendet werden. Dies bedeutet, dass der Zähler systematisch die Bitfolgen einer vorgegebenen Länge  $2^n$  (n: Anzahl der Eingänge der Schaltung) durchläuft, so dass alle möglichen Eingangsstimuli einer kombinatorischen Schaltung erzeugt werden. Beim Aufwärtszähler werden alle Testmuster der Reihe nach erzeugt und sind einfach nachvollziehbar, da sie mathematisch immer binär um 1 addieren. Desgleichen wird beim Abwärtszähler immer binär um 1 subtrahiert. Charakteristisch bei diesem Zähler ist, dass zwar die höherwertigen Bits (MSB) sehr wenig schalten, dafür aber das niedrigste Bit (LSB) in jedem Takt seinen Wert von 0 auf 1 bzw. umgekehrt ändert. Mathematisch lässt sich ein solcher Zähler folgendermassen beschreiben [101]:

**Bild 4.3:** Testmustersignal eines Aufwärtszählers

- $\triangleright$  Eine Ausgangsvariable  $z_i$  ändert immer dann ihren Wert, wenn alle niedrigeren Variablen  $z_{i-1} \dots z_0$  den Wert 1 besitzen und ein neuer Zählimpuls eintrifft

- $\triangleright$  Eine Ausgangsvariable  $z_i$  ändert dann ihren Wert, wenn die nächst niedrigere Variable  $z_{i-1}$  von 1 auf 0 geht

Bild 4.3 zeigt das Bitmuster eines 5 Bit Aufwärtszählers als analoges Signal.

#### 4.1.2 Gray Code Zähler

Diese Art von Zählern - auch als zyklische Binärzähler bezeichnet - zeichnen sich dadurch aus, dass sich jede Ziffer von der vorangehenden nur auf einer binären Position unterscheidet. Für die Signale auf den Leitungen bedeutet dies, dass zu jedem Takt immer nur ein digitales Signal seinen Zustand ändert, also von 1 auf 0 bzw. von 0 auf 1 schaltet.

Bild 4.4 zeigt das Analogsignal eines 5 Bit Gray Code Zählers. Die ersten 10

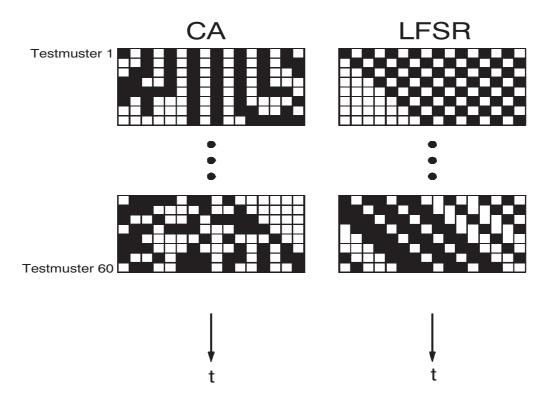

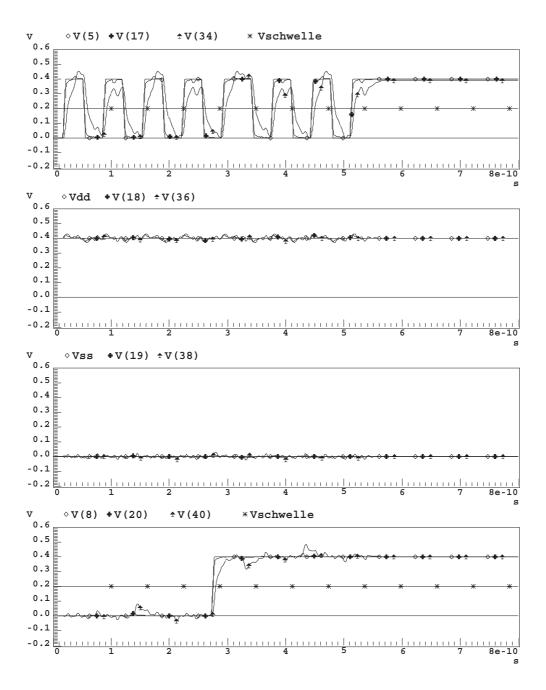

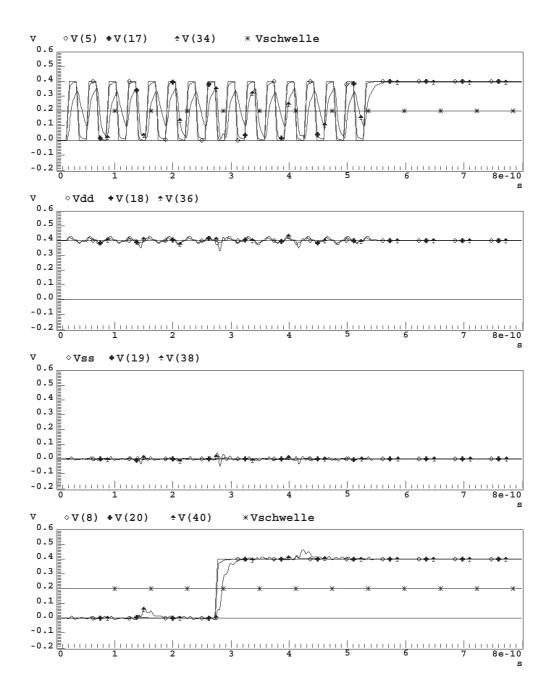

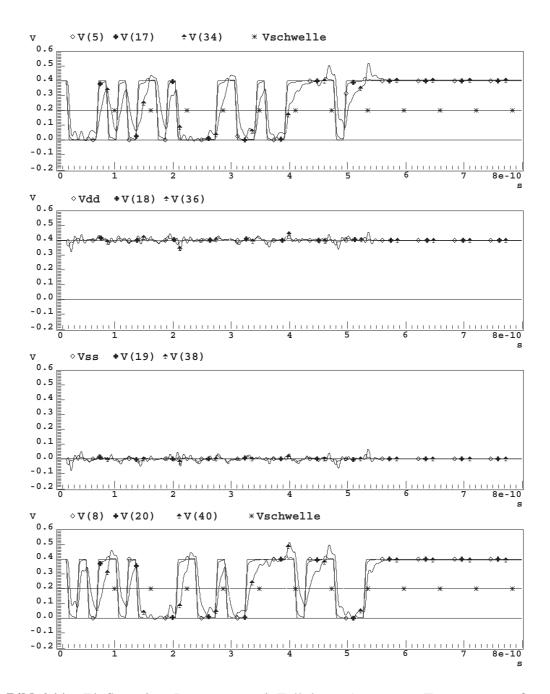

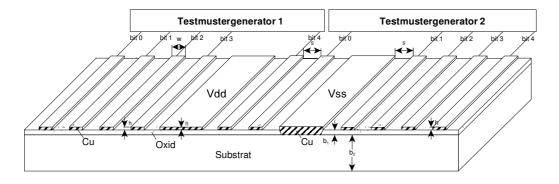

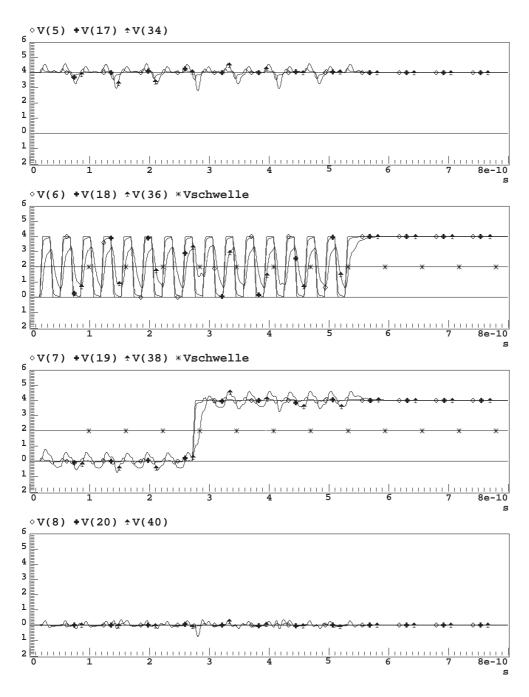

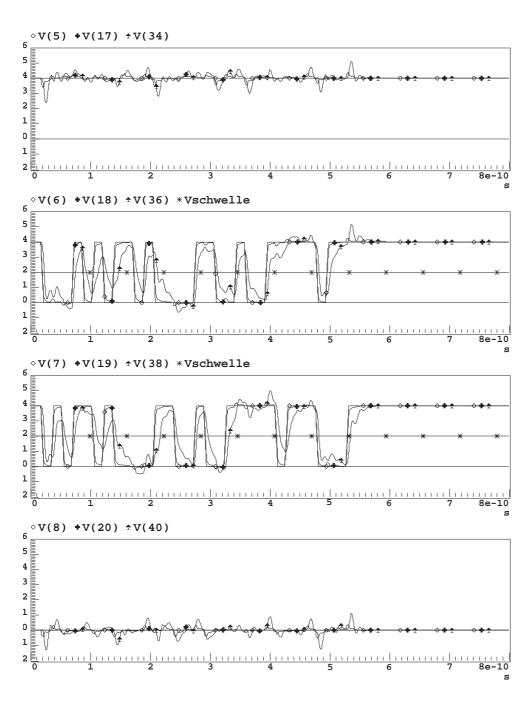

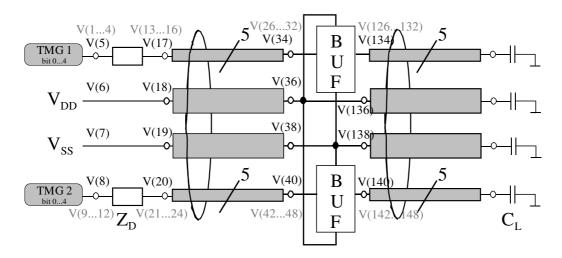

**Bild 4.4:** Testmustersignal eines Gray Code Zählers