it 2/2006

# EDA – Eine Voraussetzung für die Nanoelektronik<sup>1</sup>

EDA – a Precondition for Nanoelectronics<sup>2</sup>

Dieter Treytnar, Ralf Popp, edacentrum GmbH, Hannover

**Zusammenfassung** Der fehlerfreie und effiziente Entwurf von hochkomplexen Chips mit oft mehr als 100 Millionen Transistoren ist heute eine der größten Herausforderungen beim Chip-Design. Ohne Entwurfsautomatisierung (Electronic Design Automation, EDA) ist sie nicht zu bewältigen. Um die hierzu notwendigen intensiven Forschungsarbeiten voranzutreiben, fördert das BMBF diesen Bereich in hohem Maße und hilft damit deutsche Kernkompetenzen wie Automotive und Tele-

kommunikation voranzutreiben.

Summary Today the faultless and efficient design of high-complex chips with often more than 100 million transistors is one of the biggest challenges in chip design. This cannot be mastered without Electronic Design Automation (EDA). To speed up the necessary intense research, the BMBF promotes this area highly and thus helps to speed up German core competences like automotive and telecommunication.

**KEYWORDS** B.7 [Integrated Circuits] EDA, Electronic Design Automation, Entwurfsautomatisierung, microelectronics, Mikroelektronik, nanoelectronics, Nanoelektronik, chip design, Chipentwurf

#### 1 Die Zukunft der Mikroelekektronik

Alle, die sich mit Mikroelektronik beschäftigen, bewegt die Frage: Wie geht es weiter - können wir das exponentielle Wachstum, das seit mehr als 30 Jahren anhält, fortsetzen und: Was ist das größte Problem auf dem Weg zu den Super-Chips der Zukunft? Ziemlich deutlich sehen wir, dass weitere Fortschritte in der Fertigungstechnologie den bisher Jahr für Jahr für Jahr erreichten Komplexitätsanstieg von ca. 60% noch mindestens für weitere 15 Jahre möglich machen werden. Dabei wird vielfach übersehen, dass es zum Markterfolg nicht ausreicht, allein die Fertigungstechnologie bereitzustellen. Chips müssen, bevor sie gefertigt werden kön-

nen, entworfen werden und dies im Zeichen immer kleiner werdender Produktlebenszyklen - in immer kürzeren Zeiten. Zunehmend liegt auch die größte Wertschöpfung eines Chips im Entwurf: Ein Mikroprozessor hat z. B. einen wesentlich höheren Wert als ein auf der gleichen Linie gefertigter Chip gleicher Größe mit einfachen logischen Schaltkreisen oder gar ein Speicherchip. Immer mehr fragen wir uns aber, ob wir beim Entwurf mit der rasanten Entwicklung der Fertigungstechnik Schritt halten können. Werden wir möglicherweise einen Punkt erreichen, wo wir sagen müssen: Wir können unsere Super-Chips zwar fertigen, aber in endlicher Zeit entwerfen können wir sie leider nicht. Das wäre dann etwa so, als könnten wir das dickste Buch der Welt zwar drucken und binden, aber der Inhalt bestünde nur aus Gedankenstrichen.

Grundsätzlich kann man versuchen, dieses Problem durch erhöhten Arbeitseinsatz, also größere Entwicklungsteams zu lösen. Dieser Ansatz stößt jedoch schnell an unüberwindliche Grenzen. Chips großer Komplexität werden heute von Teams mit mehr als hundert Ingenieuren entworfen. Der dabei auftretende Aufwand für die Koordination und das Projektmanagement senken die Effizienz erheblich. Zudem ist dieser Ansatz mit erheblichen Risiken für den Entwicklungserfolg verbunden. Es ist klar, dass auf diesem Wege kaum weiter fortgeschritten werden kann.

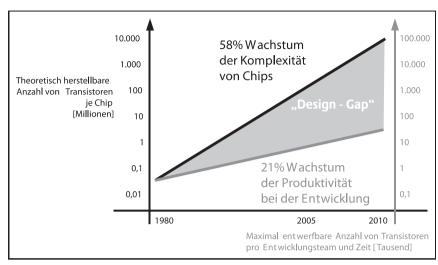

Eine Lösung des Problems, das auch als Entwurfslücke (engl.: design gap) (siehe Bild 1) bekannt geworden ist, kann nur durch eine drastische Steigerung der Entwurfsproduktivität gelingen. Der dazu notwendige Hebel wird durch angepasste Entwurfsmethoden und

<sup>&</sup>lt;sup>1</sup>EDA-Forschung in Deutschland mit dem edacentrum

<sup>&</sup>lt;sup>2</sup>EDA-Research in Germany with edacentrum

**Bild 1** Die Entwurfslücke öffnet sich scherenartig: Die Komplexität (Zahl der Transistoren) der herstellbaren Chips wächst mit den Jahren viel schneller als dies im Chipentwurf umgesetzt werden kann. Ohne eine (Teil-)Kompensation durch bessere EDA-Software werden wir hochkomplexe Chips zwar fertigen, aber nicht entwerfen können.

-werkzeuge (Software) zur Automatisierung des Entwurfs (Electronic Design Automation, EDA) bereitgestellt. Wenn also die Herausforderungen, die die Fertigungstechnologie dem Entwurf stellt, bewältigt werden sollen, dann muss stärker als bisher in die Entwurfsautomatisierung investiert werden. Dies war im Übrigen schon immer so und ist in allen Branchen gleich. Produktivitätssteigerung bedeutet Automatisierung. EDA ist der entscheidende Schlüssel zur Zukunft der Nanoelektronik. Nur durch EDA wird es gelingen, die Schaltungskomplexität zu bewältigen, die Entwurfsproduktivität im erforderlichen Maße zu steigern und die Entwurfsqualität zu verbessern.

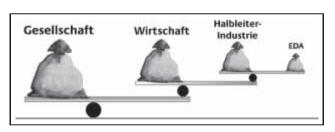

Die Welt von EDA ist heute klein, noch viel kleiner als die Welt der Nanoelektronik - ganze 3 Mrd. Dollar werden weltweit umgesetzt, davon bestenfalls 300 Mio. Euro in Deutschland. Der entsprechende Industriezweig hat sich - seit etwa 1980 - fast ausschließlich in den USA entwickelt. Er bildet, trotz seiner relativ geringen Größe, die entscheidende Grundlage für den Erfolg der gesamten Nanoelektronik, der davon abhängigen Geräte- und Systembranchen und damit ganzer auf solche Industrien gegründeter Volkswirtschaften (siehe Bild 2).

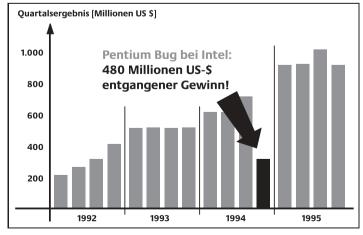

Was passiert, wenn man die Entwurfsmethodik unterschätzt, zeigt der berühmte Pentium-Bug (Bild 3), der der Firma Intel 1994 fast 500 Mio. Dollar Ergebnisverlust bescherte. Dies war ein Entwurfsfehler, der aufgrund unvollständiger Simulation unentdeckt blieb.

Mit der sich öffnenden Schere des Design-Gaps verschlimmert sich die Situation von Jahr zu Jahr. Dennoch ist es bisher nicht gelungen, dem Thema EDA die erforderliche Aufmerksamkeit zu verschaffen. Der Grund dafür ist einfach. Investitionen in Fertigungstechnologie erscheinen logisch und unvermeidbar. Viel Geld floss beispielsweise in die Zukunftsthemen Lithographie (Röntgen), Scheibendurchmesser (300 mm) und Fertigungen (Dresden). Dagegen erscheinen Investitionen in Designtechnologie abstrakt und vermeidbar und immer wieder hören wir die Scheinargumente wie: Was ist denn eigentlich das Ergebnis von EDA? Ihr habt doch Eure Chips bisher immer entwerfen können, warum soll sich das plötzlich ändern?

Im verschärften Wettbewerb der Mikroelektronikindustrie werden solche Firmen und Länder erfolg-

**Bild 2** EDA wirkt über einen Hebel auf die Gesellschaft: Mit wenig Kraft- bzw. Finanzaufwand werden die weiteren Teile der Wertschöpfungskette in Gang gesetzt.

**Bild 3** Dargestellt sind die Quartalsergebnisse in Millionen Dollar über der Zeit. Der durch einen Entwurfsfehler, den so genannten "Pentium-Bug", verursachte Umsatzeinbruch ist deutlich zu erkennen.

reich hervorgehen, die frühzeitig ihren Fokus auf das Thema EDA – also Entwurfsfähigkeit, Entwurfsmethodik und Entwurfsproduktivität gerichtet haben. Vom BMBF geförderte Initiativen haben Kompetenzen auf dem EDA-Gebiet geschaffen, die sich durch eine enge Beziehung zwischen Forschern, Anwendern und Vermarktern auszeichnen. Für die Lösung der zukünftigen Aufgaben reicht jedoch die Durchführung einzelner Projekte nicht mehr aus. Die Schwierigkeit der anstehenden Aufgaben verlangt eine konzertierte Aktion und neue Modelle der Zusammenarbeit.

# 2 Ohne EDA keine Chips – wo EDA begann

Mit der Gründung der Firma Mentor Graphics durch Tom Bruggere im Jahre 1981 wird gern, obwohl dies nicht die erste EDA-Firma war, die Geburt der EDA-Industrie verbunden. Aber schon 1964 haben sich offenbar Forscher und Entwickler getroffen, um Neues zum Thema Design Automation zu präsentieren und Erfahrungen auszutauschen. Wo liegen also die Wurzeln von EDA?

Erste EDA-Programme entstanden vor ca. 40 Jahren zeitlich parallel sowohl in der Mikroelektronik als auch in der (noch diskreten) digitalen Elektronik, deren Träger die Leiterplatte war. In der Mikroelektronik, die sich nach der Präsentation des ersten ICs durch Jack Kilby im Jahre 1958 sehr schnell entwickelte. standen zunächst die (aus heutiger Sicht) niedrigen Entwurfsebenen im Vordergrund des Interesses. Es ging darum, die halbleiterphysikalischen Prozesse zu verstehen und daraus Erkenntnisse für die Gestaltung einzelner Bauelemente zu gewinnen: Prozess- und Devicesimulatoren entstanden. Sehr bald ergab sich auch die Notwendigkeit, das Verhalten ganzer (noch sehr kleiner) Schaltungen vorhersagen und analysieren zu müssen. Erste Netzwerkanalyseprogramme mit speziellen Modellen für integrierte Transistoren kamen auf. SPICE (Simulation Program with Integrated Circuit Emphasis, 1972) ist der große Meilenstein, der im Gedächtnis haften geblieben ist.

Gleichzeitig entstanden im Bereich der Entwicklung digitaler Großrechenanlagen die ersten Programme zur Logiksimulation und zur Anordnung und Verdrahtung von Komponenten auf Leiterplatten. All dies entstand nicht etwa in spezialisierten Softwarefirmen, sondern in den Labors der Halbleiterbzw. der Datenverarbeitungsindustrie und vor allem in den Universitäten und anderen staatlichen Forschungseinrichtungen. Die Basis dafür waren die enormen Fortschritte in der Ingenieurmathematik, die mit dem Vordringen der elektronischen Datenverarbeitung eingesetzt hatten, insbesondere auf Gebieten wie numerische Lösungsverfahren, kombinatorische Optimierung und graphische Datenverarbeitung. Hier, in der Grundlagenarbeit der Jahre 1960 bis 1970 liegen die eigentlichen Wurzeln von EDA. Interessanterweise kamen zahlreiche wichtige Beiträge in diesen Jahren aus Europa, das in dieser Zeit und den darauf folgenden Jahren eine wichtige Rolle gespielt hat. Kennzeichnend für diese Phase, die etwa bis 1980 andauerte, war die enge, unmittelbare Zusammenarbeit zwischen Universitäten und Industrie, zwischen Forschern und Anwendern. Obwohl diese von beiden Seiten als außerordentlich fruchtbar empfunden wurde, fehlte zum dauerhaften Erfolg eine wesentliche Komponente. Die entwickelten Programme waren letztlich Prototypen für Spezialisten. Mit dem fortschreitenden Wachstum der Mikroelektronikund Systemindustrie wurden robuste, wartbare Programme mit intuitiven Benutzeroberflächen für (relativ) unerfahrene Anwender benötigt, was aber keine Aufgabe für Universitäten war.

An dieser Stelle entwickelte sich konsequenterweise eine spezifische Softwareindustrie (die zunächst noch dedizierte Hardware als Last mit sich herumschleppte) und versprach, dieses Problem zu lösen. Die Not der Anwender und ihre steigende Zahl ließ sie ein schnelles Geschäft und hohe Stückzahlen wittern. In der Tat ist die Zahl der beispielsweise durch die Firma Daisy reich gewordenen durchaus beträchtlich, obwohl die ersten Workstations aus heutiger Sicht lediglich schnell zusammengesteckte Systeme mit – gegenüber dem Stand der Forschung - einfachen Programmen zur Schaltungseingabe, zur Logiksimulation und (später) zur interaktiven Layouterstellung gewesen sind.

Mit dem Erfolg von Daisy, Mentor und Valid war das EDA-Band zwischen Universitäten und Anwenderindustrie zerschnitten. Die EDA-Industrie, als neuer potentieller Partner der Forschung, konzentrierte sich auf Umsatz und Ergebnis und dachte (noch) nicht an neue, revolutionäre Werkzeuge. Interessanterweise begann gerade jetzt an den Universitäten (auch und gerade in Europa) eine Blütezeit der EDA-Forschung. Das Thema war hochattraktiv, die Fördergeber hatten seine Bedeutung erkannt und überall schossen Forschergruppen aus dem Boden. In Deutschland etablierte sich das EIS-Projekt (Entwurf Integrierter Schaltungen), das dank großzügig bereitgestellter Mittel viele an einen Tisch brachte und sich neben seinen EDA-Aktivitäten große Verdienste erwarb, indem es die Ausbildung im Schaltungsentwurf an Universitäten systematisch förderte. In einem (zu) späten Versuch, das Thema EDA-Entwicklung im eigenen Hause zu forcieren, unterstützte auch die Siemens AG das Projekt massiv, wenn auch dieser Versuch letztlich an der Kraft der nunmehr etablierten (amerikanischen) EDA-Industrie scheiterte. Auf europäischer Ebene wurde EDA großzügig gefördert. Mehrere große Projekte befassten sich mit Frameworks, Synthese, Analogentwurf, Test, usw. Trotz zahlreicher Einzelerfolge gelten heute diese Aktivitäten der 80er-Jahre weitgehend als Flop. Konsequenterweise nahmen deshalb

die öffentlichen Hände ihre Förderung zu Beginn der 90er-Jahre drastisch zurück.

Was war geschehen? Ähnlich wie in den Kernbereichen der Mikroelektronik hatte Europa auch bei EDA wesentliche Grundlagenarbeit geleistet, jedoch war es nicht gelungen, diese in wirtschaftliche Erfolge umzuwandeln. Ob dies an der typisch europäischen (deutschen?) Umsetzungsschwäche liegt, die mit Technikverliebtheit, Vernachlässigung von Marketing, mangelnder Risikofreude, fehlendem Unternehmertum usw. zu tun hat, ist möglich. In den amerikanischen EDA-Firmen sitzen wie selbstverständlich die führenden Köpfe der Wissenschaft auch in den Management-Boards. Firmen wie Cadence oder Synopsys wären ohne ihre Verbindungen zur Forschungsszene nie das geworden, was sie heute sind. In Europa, speziell in Deutschland, ist die Verknüpfung von Forschungstätigkeit und Geschäftsinteresse fast anrüchig, auf jeden Fall aber selten. So ist denn der Platz der Professoren bestenfalls im "Technical Advisory Board", da, wo man sich abseits des Geschäftes auf technische Fragen konzentrieren kann.

Spätestens 1995 war jedenfalls klar, dass sich eine bedeutende europäische EDA-Industrie nicht entwickeln würde. Das Thema verlor deutlich an Attraktivität und viele Forschungsaktivitäten an den Hochschulen wurden eingestellt. Gleichzeitig erkannte die Mikroelektronikindustrie, dass zur Sicherstellung der Designfähigkeit erneut größere eigene Anstrengungen nötig sein würden, denn EDA hatte begonnen, sich anwendungsspezifisch zu entwickeln. Das Rezept "Alles was ich brauche, kann ich bei EDA-Firmen kaufen", seit 1980 das Erfolgsmodell, wurde erneut in Frage gestellt und führende Firmen, wie IBM, Intel und LSI investierten wieder verstärkt in die Entwicklung eigener EDA-Werkzeuge.

Es gibt positive Anzeichen, dass sich die Erkenntnis der Anwender, zur Sicherstellung der Designfähigkeit bei EDA größere eigene Anstrengungen unternehmen zu müssen, ständig weiter verbreitet. Von den drei zentralen EDA-Aufgaben: Beherrschung der Komplexität, Steigerung der Produktivität und Verbesserung der Qualität hat sich schließlich in fast 40 Jahren Geschichte keine erledigt. Häufig vergessen wir wegen der Dringlichkeit der Themen Komplexität und Produktivität, dass das Qualitätsproblem (wobei darunter sowohl die Qualität des Entwurfs, aber durchaus auch die Qualität der Entwurfssoftware verstanden werden kann) die größte Herausforderung darstellt. Hier liegt ein Potential, dessen Ausschöpfung noch in weiter Ferne liegt. Dabei sind nicht nur Fragen heterogener Systeme, die Verhaltenssynthese oder formale Spezifikationsmethoden von Interesse, nein, das gesamte Spektrum von EDA über alle Entwurfsebenen hinweg ist und bleibt Forschungsthema und damit auch für die Anwenderindustrie eine wichtige dauerhafte Vorfeldaufgabe. Eine kontinuierliche öffentliche Förderung, die sich allerdings auch auf langfristige Projekte erstrecken muss, kann dabei - sinnvoll genutzt - außerordentlich hilfreich sein. Sparen bei EDA setzt dagegen die eigene Designfähigkeit aufs Spiel und gefährdet langfristig den Geschäftserfolg bei Mikroelektronikproduk-

In Deutschland ist es dem Bundesministerium für Bildung und Forschung (BMBF) zu verdanken, dass zur Stimulation der Forschung wieder Fördermittel in größerem Umfang bereitgestellt wurden. Damit konnten in den letzten Jahren beachtliche – auf den unmittelbaren Bedarf der deutschen Halbleiterindustrie zugeschnittene – Ergebnisse erzielt werden.

Die JESSI-Initiative, sowie der in den Jahren 1997 bis 2000 vom BMBF geförderte Schwerpunkt "Smart System Engineering", haben Kompetenzen auf dem EDA-Gebiet geschaffen, die sich durch eine enge Beziehung zwischen Forschern, Anwendern und Vermarktern auszeichnen. Für die Lösung der zukünftigen Aufgaben reicht jedoch die Durchführung einzelner Projekte nicht mehr aus. Die Schwierigkeit der anstehenden Aufgaben verlangt eine konzertierte Aktion und neue Modelle der Zusammenarbeit.

Im Rahmen des Smart-System-Engineering-Industriearbeitskreises (SSE-AK) wurde deshalb ein Konzept für einen neuen EDA-Forschungsschwerpunkt ASEDA (Application Specific Electronic Design Automation) entworfen, das eine Reihe von sorgfältig aufeinander abgestimmten F&E-Projekten zur Förderung vorschlug. Dabei entstand die Idee, zur Erreichung maximaler Ergebnisse neue Kompetenzen und Netzwerke aufzubauen, um den geplanten Förderschwerpunkt zu begleiten. Die Industrie hat deshalb Anfang 2001 die Initiative zur Einrichtung eines deutschen EDA-Zentrums ergriffen.

## 3 Die Gründung des edacentrum

Das edacentrum ist eine unabhängige Institution zur Förderung von Forschung und Entwicklung auf dem Gebiet Electronic Design Automation. Es versteht sich als zentrale Anlaufstelle für Fragen der Entwurfsautomatisierung und organisiert gemeinsame Aktivitäten von System- und Hableiterherstellern, EDA-Anbietern und Forschungseinrichtungen. Das edacentrum initiiert, begutachtet und begleitet industriegeführte EDA-F&E-Projekte. Darüber hinaus fördert es die Bündelung vorhandener EDA-Kompetenz an deutschen Forschungseinrichtungen durch die Stimulation von EDA-Clusterforschungsprojekten und von EDA-Netzwerken. Und es betreibt Öffentlichkeitsarbeit mit dem Ziel, die Entwurfsautomatisierung als zentralen Lösungsgedanken für das Komplexitätsproblem der Mikroelektronik im höheren Firmenmanagement, in der Politik und in der Öffentlichkeit stärker transparent zu machen.

Aktuell sind mehr als 50 Firmen Mitglied im edacentrum, darunter Infineon, Bosch, Nokia, Philips, Atmel, diverse Universitäten und Forschungseinrichtungen und viele andere mehr (siehe Bild 4).

Seinen Mitgliedern bietet das edacentrum vielschichtige Informationen mit praktischem Nutzen. In dem vierteljährlich erscheinenden Newsletter wird über neueste Forschungsergebnisse, Projekterfolge, Konferenzen, Personalien und Partnerfirmen berichtet. Jährlich erstellen Mitarbeiter des edacentrum einen umfangreichen Trendbericht von der weltgrößten Design-Konferenz, der Design Automation Conference (DAC) und verteilen diesen an die Mitglieder. Das Netzwerk gilt mittlerweile als das größte EDA-Netzwerk Deutschlands. Innerhalb der umfassend zum Thema EDA in Deutschland informierenden Internetseiten des edacentrum wurden mit dem "edaAtlas" und dem "edaKalender" zwei besonders für die EDA-Forschung wichtige Informationsplattformen geschaffen:

Durch den edaAtlas [8] werden stetig aktualisierte Informationen zur Forschung und Entwicklung von EDA zentral zur Verfügung gestellt. Damit wird das Ziel verfolgt, das Kompetenznetzwerk der EDA-

Experten zu stärken und den Informationsaustausch zu verbessern. Die bereitgestellten Daten beinhalten Informationen zu Publikationen, Werkzeugen, Projekten, Forschungsthemen und Lehrangeboten sowie Forschungseinrichtungen. Der edaAtlas befindet sich derzeit noch in der Aufbauphase und umfasst Daten von ca. 1500 Organisationen und Einrichtungen mit dem Schwerpunkt in Deutschland. EDA-Experten sind im Sinne eines sich kontrolliert erweiternden Netzwerkes dazu aufgefordert, bei der Pflege des Informationsportals mitzuwirken, um das Informationsangebot und die Funktionalität kontinuierlich zu verbessern.

Der edaKalender [5] bietet einer inzwischen beachtlich großen Fangemeinde Informationen über derzeit mehr als 800 Konferenzen, Workshops, Symposien und Messen im Bereich EDA in deutscher und englischer Sprache. Jede Konferenz ist mit einer Kurzbeschreibung, dem Veranstaltungsort- und Termin, der Internetadresse, der "Submission-Deadline" und einigen Stichwörtern im Konferenzkalender eingetragen. Konferenzen können nach Kategorien (Kürzel, Name, URL, Beginn, Ende, Deadline, Ort und Land) gesucht und sortiert angezeigt werden. Außerdem gibt es Suchmasken zu Kürzeln, Ländern und Zeiträumen, die beliebig miteinander kombinierbar sind. Der Konferenzkalender wird stetig gepflegt, profitiert aber insbesondere auch von der Mithilfe seiner Nutzer.

Im Rahmen einer erfolgsabhängigen anteiligen Aufwandsentschädigung initiiert, begutachtet und begleitet das edacentrum industriegeführte EDA-F&E-Projekte. Dazu werden beteiligte Partner durch Projektkoordination, Beratung, Veranstaltungsorganisation sowie Öffentlichkeitsarbeit von ihren administrativen Aufgaben entlastet und können sich somit stärker mit den eigentlichen Forschungstätigkeiten befassen.

Zusätzlich zu den geschilderten Leistungen bietet das edacentrum weitreichende, individuelle, kostenpflichtige Dienstleistungen rund um Chip-Entwicklungsprozesse und F&E-Projekte. Dazu zählen Projektmanagement für F&E-Projekte, innovative EDA-Lösungen, EDA-Kompetenzentwicklung und Prozessoptimierung.

Jährlich organisiert das edacentrum in Deutschland zwei EDA-Veranstaltungen, das edaForum und den Ekompass-Workshop.

Das edaForum [7] ist ein an Entscheidungsträger aus der Industrie gerichteter Kongress, auf dem diese mit hochrangigen Wissenschaftlern aus aller Welt zusammentreffen. Diskussionsthema sind die Investitionen in EDA, welche zur Zukunftssicherung der Basistechnologie Mikroelektronik erforderlich sind. Das edaForum soll damit dazu beitragen, die Marktposition von System- und Halbleiterfirmen in Deutschland zu stärken und damit Arbeitsplätze zu sichern. Auf der Veranstaltung werden gleichrangig neben technischen auch ökonomische Themen behandelt. Die Bandbreite der Vortragsthemen reicht von der Ausbeute bei der Halbleiterfertigung über Fragen der Design-Verifikation bis zum Thema "Design für Profitabilität". Zu den Referenten gehörten in den letzten Jahren Tom DeMarco, Richard Newton, Al-

Bild 4 Das edacentrum und seine Mitglieder – Das deutsche EDA-Kompetenz-Netzwerk.

berto Sangiovanni-Vincentelli, Daya Nadamoudi, Rob Rutenbar, Tom Williams, Brian Bailey, Raul Camposano, Wojciech Maly, Grant Martin, Giovanni De Micheli, Andrew B. Kahng, Jacques Benkoski und andere.

Die unter dem Namen Ekompass-Workshop [6] bekannt gewordene Veranstaltung richtet sich demgegenüber eher an die EDA-Entwickler und -Anwender. Ekompass ist eine Abkürzung für den vom Bundesministerium für Bildung und Forschung (BMBF) eingerichteten Förderschwerpunkt "Entwurfsplattformen komplexer angewandter Systeme und Schaltungen". Dort werden aktuelle Forschungsprojekte und deren wichtigste Ergebnisse von Referenten aus Wirtschaft, Forschung und Politik dargestellt. Im Mittelpunkt stehen dabei technische Themen aber auch die wirtschaftlichen Auswirkungen der Projekte. Das Workshop-Programm ist mehr als eine Anreihung von Projektvorträgen, weil es durch eine parallel angelegte Ausstellung vielfältige Diskussionsmöglichkeibietet. Schon allein wegen ten hervorragenden Möglichkeider ten zum Austausch ist der jährlich im Frühiahr in Hannover stattfindende Workshop seit längerem ein Pflichttermin für alle Teilnehmer, Mitarbeiter und Interessenten rund um die vom edacentrum betreuten Ekompass-Projekte.

Innerhalb der Ausstellung der Projektergebnisse wird den Mitgliedsfirmen des edacentrum die Gelegenheit gegeben, ihre neuesten Entwicklungen an eigenen Ständen zu präsentieren. Ebenso ist der so genannte Kooperationsmarkt in die Gesamtausstellung integriert. Dabei präsentieren Forschungseinrichtungen ihre Tätigkeiten, um Firmen zu gewinnen, die sie als Projektpartner oder Unterauftragnehmer in Förderprojekten integrieren könnten.

## 4 Forschungs- & Entwicklungsprojekte

Die Zusammenarbeit der Projektpartner innerhalb des Projektes als auch mit anderen Projekten ist ein wesentlicher Punkt, um den Transfer von Ergebnissen und Know-How zu sichern und die Qualität der Ergebnisse anzuheben. Die Koordination von F&E-Projekten sowie EDA-Clusterforschungsprojekten ist die Netzwerkaufgabe, für die das edacentrum vor 4 Jahren gegründet wurde.

F&E-Projekte behandeln Aufgabenstellungen, die aus den Anforderungen der deutschen Industrie und vor dem Hintergrund der internationalen Entwicklung erwachsen. Firmen oder das edacentrum unterbreiten Vorschläge für notwendige Forschungs- und Entwicklungsarbeiten, die im Interesse der deutschen Volkswirtschaft durchgeführt werden sollten und kurzfristig zu wirksamen Ergebnissen führen. In den Halbleiterfirmen und Designhäusern finden die dabei entstehenden Projektergebnisse unmittelbar Eingang in neue Chipentwicklungen und regen darüber hinaus eigene Anstrengungen auf den erforschten Gebieten an.

Die zur Zeit vom edacentrum betreuten F&E-Projekte gehören zu dem, schon oben angesprochenen, vom BMBF zur Stimulation von EDA-Forschungsaktivitäten eingerichteten Förderkomplex namens Ekompass. In diesem Förderkomplex arbeiten deutsche Mikroelektronik-Unternehmen, EDA-Anbieter und Forschungseinrichtungen gemeinsam an der Lösung aktueller und zukünftiger Probleme im elektronischen Schaltungsentwurf.

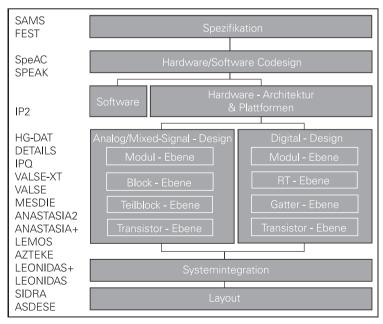

Die Arbeitsgebiete der vom edacentrum betreuten Projekte umfassen alle Ebenen des Chipentwurfs (siehe Bild 5).

Im Folgenden wollen wir einige der vom edacentrum betreuten Projekte kurz vorstellen:

Einer der treibenden Faktoren zur Anwendung mikroelektronischer Systeme ist die Steigerung der Sicherheit und des Komforts durch intelligente Assistenten, insbesondere in der Automobil- und Kommunikationstechnik. Studien kamen zum Ergebnis, dass mehr als 50% der Unfälle bei einer zeitlich vorverlegten Fahrerreaktion vermieden werden können, sodass mit einer enormen Steigerung der Sicherheit durch Fahrerassistenzsysteme zu rechnen ist. Eine hohe Komplexität sowie steigende Mobilitätsanforderungen und ein hoher Kostendruck zwingen zu einer stetigen

**Bild 5** Das Bild zeigt Entwurfsvorgänge des Schaltungsentwurfs auf verschiedenen Abstraktionsebenen. Anhand der Position der Kurztitel der Ekompass-Projekte ist die weite Abdeckung der Thematik durch den Förderkomplex erkennbar.

Miniaturisierung und einer Minimierung des Leistungsverbrauchs. Dies führt somit zu einer Integration kompletter Systeme auf einem einzigen Chip (so genannte Systems-on-Chip, kurz SoCs). Dabei entwickelt sich die zurückbleibende Produktivität des Entwurfsprozesses zunehmend zum hemmenden Faktor. Im Projekt SPEAC (Spezifikation und Algorithmus/Architektur-Codesign für hochkomplexe Anwendungen der Automobil- und Kommunikationstechnik) konnten eine Vielzahl aussichtsreicher Ergebnisse erzielt werden. Hierzu wurde ein auf vordefinierten Plattformen agierender Hardware/Software-Codesign-Ansatz zu einer plattformbasierten Algorithmus/Architektur-Codesign-Methodik für heterogene Systeme abstrahiert. Dies führt nicht nur zu einer weiteren Produktivitätssteigerung, sondern auch zu einer wesentlichen Erhöhung der Anwendungsbreite des zu entwickelnden Entwurfsflusses. Durch die weitgehende Vermeidung von Redesigns werden eine Halbierung der Entwurfszeit bei gleichzeitig steigender Komplexität, eine zwei- bis dreifache Steigerung der Produktivität, eine Senkung der Entwurfskosten um bis zu 50% sowie eine 33%-50% frühere Markteinführung im weltweiten Wettbewerb gewähr-

In einer ähnlichen Richtung arbeitet das Projekt IP2 (Intellectual Property Prinzipien für konfigurierbare Basisband SoCs in Internet-Protokoll basierten Mobilfunknetzen), das auf neuartige EDA-Methoden und Produkte für zukünftige Generationen von Mobilfunksystemen abzielt. Arbeitsinhalte sind die Erforschung neuartiger anwendungsspezifischer CAE-Methoden, wie angepasste Prinzipien des Intellectual Property (IP) und architekturgenaues Prototyping sowie ihre produktive Verwertung bei der Ausarbeitung und Optimierung neuartiger konfigurierbarer System-on-Chips. Diese sollen in zukünftigen Internet-Protokoll-basierten Mobilfunknetzen zum Einsatz kommen.

Unterstützt werden sowohl existierende GSM-basierte Netzwerke und ihre GPRS-Derivate, als auch neue UMTS-basierte und Hiperlan-Lösungen, um mobile Datenraten von weit über 2 Mb/s zu erzielen. Dabei soll die Wettbewerbsfähigkeit durch das Setzen von Standards in diesem Bereich erfolgreich umgesetzt werden.

Grundsätzlich besteht beim Entwurf nanoelektronischer Schaltungen die Forderung nach höherer Produktivität im Schaltungsentwurf mit EDA-Werkzeugen. Die Kenntnis der Produktivität ist hierbei zwingend notwendig, um die Planbarkeit von Entwicklungsprojekten zu erhöhen. Das Projekt PRODUK-TIV+ (Referenzsystem zur Messung der Produktivität beim Entwurf nanoelektronischer Systeme) leistet durch die Ermittlung der Produktivität einen wesentlichen Beitrag, Entwicklungsprojekte erfolgreich zu planen und zum Abschluss zu bringen. Die verbesserte Planbarkeit bewirkt, dass ein steigender Teil der Projekte zu Erfolg und Profit eines Unternehmens beiträgt. So trägt nicht nur die Steigerung der Produktivität, sondern auch eine verbesserte quantitative Bestimmung zur Sicherung der Entwicklungsstandorte in Deutschland nachhaltig bei. Eine gezielte Steigerung der Produktivität bedingt, dass vorab ermittelt werden kann, welchen quantitativen Einfluss eine Steigerungsmaßnahme haben wird. Nur durch Kenntnis der Produktivität im Schaltungsentwurf kann der Erfolg von EDA-Investitionen zur Erhöhung der Entwurfsfähigkeit auch betriebswirtschaftlich kalkuliert werden. Bislang ist die quantitative Beurteilung von entwickelten oder geplanten Verbesserungen der Werkzeuge und Methoden nicht gelöst. In der Halbleiterindustrie gibt es kein Bewertungsmodell und keine Methodik zur Ermittlung der Entwurfsproduktivität, die hinreichend präzise wären, um die angestrebte Objektivierung von Entscheidungen im EDA-Bereich zu ermöglichen. Das Vorhaben hat sich daher zum

Ziel gesetzt, die notwendige quantitative Messung und vorausschauende Abschätzung der Produktivität zu ermöglichen.

Ebenfalls Verfahren zur Produktivitätssteigerung beim Systementwurf in der Mikroelektronik widmet sich das Projekt IPQ (IP-Qualifikation für effizientes Systemdesign). Ansatz ist der konsequente Einsatz wiederverwendbarer Komponenten. Das rasante Innovationstempo in der Fertigungstechnologie mikroelektronischer Schaltungen erlaubt es, immer komplexere Systeme auf einem einzigen Mikrochip zu integrieren. Da sich aber im Vergleich dazu die Produktivität der Entwurfsmethoden für solche SoC nur erheblich langsamer entwickelt, steigen Entwicklungsaufwand und -dauer stark an und das bei zunehmend kürzeren Produkt-Lebenszyklen und -Einführungszeiten. Für die Lösung dieser Probleme ist der konsequente Einsatz wiederverwendbarer Schaltungsmodule, so genannter IP-Module, unverzichtbar. Das Projekt IPQ setzt dort an, wo noch die mit Abstand größten Probleme bei der Realisierung dieser IP-basierten Entwurfsmethodik bestehen, bei der IP-Qualifikation. Die IP-Qualifikation adressiert die beim IP-basierten Entwurf erforderlichen Aktivitäten zur Qualitätssicherung in der kausalen Kette Entwickeln von IPs, Auswählen/Evaluieren von IPs, Einsetzen/Anpassen von IPs, und zielt damit auf die Qualitätssicherung des IP-basierten Systementwurfs unter den Anforderungen einer hohen Entwurfskomplexität, Entwurfsproduktivität und Entwurfsfehlerfreiheit bei anhaltendem Kosten- und Zeitdruck. Damit wird ein Arbeitsgebiet charakterisiert, zu dem bisher nur in sehr wenigen Teilbereichen geeignete Lösungsansätze

Der Realisierung von funkbasierten Kommunikationssystemen mit sehr hohen Übertragungsraten steht die heutige fehlende Leistungsfähigkeit und Effizienz der vorhandenen Entwurfs- und Simulationswerkzeuge, Entwurfsmethoden und der hierarchischen Systemkomponenten im Wege. Gründe hierfür sind zum einen die mangelnde Flexibilität dieser Komponenten und zum anderen nicht ausnutzbare Optimierungspotentiale bei der Partitionierung, Schaltungsentwicklung und Prozessanbindung, hervorgerufen durch die für solche Systeme unzureichende Unterstützung der CAD-Werkzeuge und Standardbauelementmodelle. Innerhalb eines SoC Entwurfsprozesses kann der Bereich Mixed-Signal Entwurf immer weniger mit dem Digital-Entwurf mithalten. Gründe hierfür sind die fehlende Skalierbarkeit von Analogschaltungen, fehlende wirksame Ansätze für eine teilautomatisierte Analogsynthese und schwierigere Rahmenbedingungen durch gestiegene Anforderungen, wie z.B. an Arbeitsfrequenzen und Bandbreite, Signal-Integrität und Verlustleistung, bei gleichzeitiger Verschlechterung der Prozessrahmenbedingungen und komplexeren Schaltungskonzepten. Eine hochfrequente Datenübertragung, die mittlerweile auch im Kraftfahrzeug Einzug gehalten hat, erfordert die Schaffung einer besonderen Entwurfstechnologie, die einerseits die Entwicklungszeit deutlich absenkt und andererseits die Planungssicherheit erhöht (Bild 6). Dadurch wird dem Time-To-Market-Gedanken Rechnung getragen und darüber hinaus das durch Marktanalysen ermittelte optimale Zeitfenster für eine Produkteinführung bedienbar. Das Projekt DETAILS (HF Design Technologie für präzise analoge IP-basierte Front-End Lösungen in höchstintegrierten Datenübertragungs-Systemen) befasst sich mit dieser Problematik.

SoCs ermöglichen fast unbegrenzte Produktinnovationen. Aber beim Entwurf solcher Chips wird die Verifikation zum begrenzenden Faktor. 60%–80% der Entwurfsaufwände entfallen auf die Verifikation. Die Projektpartner von VALSE-XT (Hochautomatisierte, zertifizierende und skalierende Validierung von System-on-Chip-Entwürfen) gehen

Bild 6 Die inzwischen allgegenwärtige Mobilkommunikation und die damit verbundene Hochfrequenztechnik betrifft das Auto in wachsendem Maße.

davon aus, dass die Unvollständigkeit der Simulation maßgeblich für das Verifikationsproblem verantwortlich ist. Die Simulation für wichtige Verifikationsaufgaben wird durch weit leistungsfähigere, spezialisierte Verfahren ersetzt, die massive Produktivitäts- und Oualitätsgewinne bringen. Aus dieser Arbeitshypothese wird das VALSE-Programm und insbesondere das Arbeitsprogramm für VALSE-XT abgeleitet. Im Projekt wird die Technik der formalen Eigenschaftsprüfung zu einer erschöpfenden, hochautomatisierten Verifikation ausgebaut, um die Korrektheit automatischer und händischer Entwurfsverfeinerungen für digitale Schaltungen und Analogzellen durch mathematische Äquivalenzvergleiche zu garantieren und durch eine vollständige Betriebsfehleranalyse kostengünstig die Robustheit sicherheitskritischer Systeme gegen Betriebsfehler zu gewährleisten.

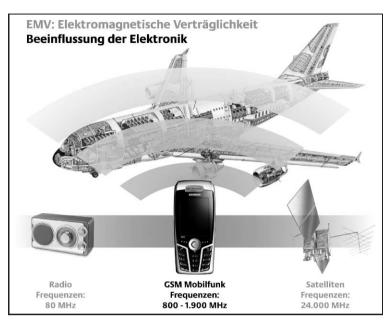

Was haben Handy und Flugzeug gemeinsam? Sie werden beide bzw. gegenseitig durch elektromagnetische Verträglichkeit (EMV) und elektrostatische Entladung (ESD) beeinflusst. Während akustische Störungen beim Handy meist noch hingenommen werden, sieht man dies schon anders, sobald man

seinen Platz im Flugzeug eingenommen hat und der Sitznachbar aufgrund seines Handytelefonates eine Störung des elektronischen Bordnetzes verursacht. Infolge der weiter fortschreitenden Miniaturisierung und der hochkompakten Aufbau- und Verbindungstechnologien (AVT) kommt es zu einer Erhöhung der Betriebsfrequenzen bei Mikroprozessoren auf ca. 10 GHz. Dies hat eine erhebliche Steigerung unerwünschter HF/EMV-Effekte zur Folge, welche in den nächsten sechs Jahren die wesentlichen limitierenden Faktoren hinsichtlich der integrierten Anwendung von IC und Packaging (HDP/HDI) sein werden. Ohne den Einsatz integrierter Werkzeuglösungen für die Modellierung und Simulation von unerwünschten Feldkopplungen auf allen Systemebenen wird daher in Zukunft eine kosten- und termingerechte Entwicklung zuverlässiger mikroelektronischer Produkte (IC, Komponente, Modul, System) nicht mehr möglich sein. Um hier Abhilfe schaffen zu können, müssen die bisher getrennt betrachteten Gebiete EMV-gerechter Systementwurf und Entwurf komplexer HF-Systeme zu einer durchgängigen Entwurfsmethodik zusammenwachsen (siehe Bild 7). Im Projekt MESDIE

**Bild 7** Jeder der fliegt, kennt es: Mobilfunkgeräte sind auszuschalten, da man nicht sicher ist, dass Beeinflussung mit katastrophalen Folgen ausgeschlossen ist.

(Effizienter Entwurf hochintegrierter mikroelektronischer Systeme und AVT-Elemente unter HF- und EMV-Aspekten) wird im Bereich Anwendungs- und Grundlagenwissen zur Thematik elektromagnetischer Kopplungen (HF/EMV/SI) auf IC- und Systemebene geforscht. Ein wesentliches Ziel besteht darin, einen Paradigmenwechsel hinsichtlich des Entwurfs von IC und Systemen (Geräte) und der üblicherweise verwendeten Entwicklungsmethoden einzuleiten. Die bisher getrennt betrachteten Gebiete EMV/SI-gerechter Systementwurf und Entwurf komplexer HF-Systeme müssen zu einer durchgängigen Entwurfsmethodik zusammenwachsen. Auf diese Weise wird der Zeitaufwand von der Produktdefinition bis zur Fertigungsüberleitung bei den in Deutschland umsatzstarken Branchen Halbleiterhersteller, Telekommunikation, Industrie- und KFZ-Elektronik reduziert.

Entwurfsmethoden zur Absicherung gegen elektromagnetische Störungen von außen widmet sich das Projekt SIDRA (Safe IC-Design for Robust Application). Ziel ist es, simulationsgestützte Methoden für moderne Halbleitertechnologien zu entwickeln, die die Ro-

bustheit von ICs gegen elektrostatische Entladungen (ESD) absichern. ESD kann sowohl in der Fertigung als auch während der späteren Nutzung auftreten und ist ein potenzieller "Chip-Killer". Die Auswirkungen der erwarteten Projektergebnisse sind die ESD-Absicherung von ICs in zukünftigen Technologien, u.a. in sicherheitskritischen Anwendungen wie Automobilelektronik, Identifikationssystemen und Chip-Karten, die Minimierung des Risikos von teuren und Image-schädigenden Problemen bei Lieferverpflichtungen oder im Feld, sowie die Erreichbarkeit von Spezifikationsforderungen, die für die Halbleiterhersteller heute aus Zuverlässigkeitsgründen nicht machbar sind.

Um die neuen Technologien und Möglichkeiten effektiv nutzen zu können, ist es dringend erforderlich, die Entwurfsautomatisierung voranzutreiben. Der Zeitaufwand für das Design analoger und Mixed - Signal - (A/MS) - Schaltungsblöcke liegt derzeit immer noch im Bereich mehrerer Monate und damit deutlich höher als für entsprechende Digitalfunktionen. Das liegt zum einen an einer unzureichenden Analogdesignmethodik, aber auch an den

durch die neuen Technologien immer dominanter werdenden parasitären Effekten und komplexeren funktionalen, z.T. interagierenden Abhängigkeiten der Bauelemente voneinander. Es muss eine wesentliche Verkürzung der Entwurfszeiten erreicht werden, um den Marktanforderungen gerecht zu werden. Gleichzeitig sind Anstrengungen im Bereich der Systemspezifikation und -verifikation erforderlich, die einen Beitrag zur Verhinderung von Redesignzyklen liefern. In System- und Halbleiterhäusern ist eine erhebliche Menge an Analog-IP vorhanden, welches in seiner jeweiligen Form und mit den bisher verfügbaren Designwerkzeugen nicht effizient wiederverwendet werden kann. Gründe dafür sind u.a. neue Prozesse, eine geänderte Spezifikation oder der Weggang eines Entwicklers. In den letzten Jahren sind gute Grundlagen für neue Designmethoden erarbeitet worden, die als Basis für eine verstärkte Wiederverwendung von Analog-IP dienen können. Das Projekt ANASTASIA (Sprachbasierter Entwurf und Reuse für Anwendungen im Mixed-Signal) arbeitet daran, durchgängige Top-Down-Entwurfsmethoden für integrierte analoge und Mixed-Signal-Systeme (A/MS-Systeme) zu entwickeln und hat erhebliche Fortschritte im Bereich der Entwurfsautomatisierung für A/MS-Systeme sowie der Wiederverwendung von Schaltungsblöcken erzielt. Die Motivation für die Arbeiten ist es, die Lücke im industriellen Entwurfsablauf zwischen Systemspezifikation und -entwurf einerseits sowie dem Schaltungsentwurf auf Blockebene andererseits zu schließen. Zu diesem Zweck wird ein in allen Ebenen von der Systemspezifikation bis zum Layout durch Werkzeuge und Entwurfsmethoden unterstützter Ablauf benötigt, der mit den im digitalen Schaltungsentwurf verfügbaren EDA-Methoden vergleichbar ist. Um dieser Forderung nachzukommen, entwickeln die Projektpartner neue Methoden und Werkzeuge. Diese ermöglichen den Top-DownEntwurf und die Bottom-Up-Verifikation von A/MS-Systemen mit Hilfe von Mixed-Mode/Mixed-Level-Simulation in einer konsistenten Entwurfs- und Simulationsumgebung. Die Projektarbeit konzentriert sich hauptsächlich auf Anwendungen aus der Automobilelektronik und der drahtlosen Telekommunikation.

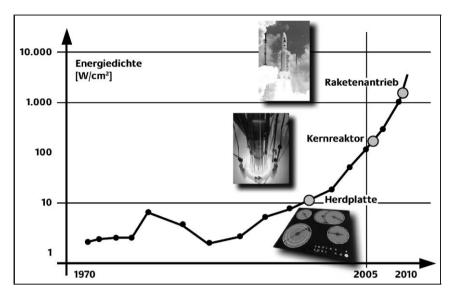

Für Multimedia-Applikationen im Rahmen des neuen Mobilfunkstandards UMTS werden Datenmengen von bis zu 2 Mbit/s verarbeitet werden müssen. Dies ist 200 mal mehr, als die Leistung derzeitiger GSM-Mobiltelefone. Diese enorme Rechenleistung wird durch stets höherfrequent ausgeführte Schaltvorgänge erbracht. Die physikalisch bedingte Verlustleistung dieser Schaltvorgänge ist heute der begrenzende Faktor zur weiteren Erhöhung der Leistungsfähigkeit integrierter Schaltungen. Obwohl seitens der Anbieter und Anwender immer mehr Applikationen im Mobiltelefon gefordert werden, muss gewährleistet sein, dass der maximale Leistungsverbrauch 3 Watt nicht übersteigt. Ziel des Projektes LEMOS (Low-Power - Entwurfsmethoden für mobile Systeme) ist die Steigerung der Entwurfsproduktivität durch Verringerung der Zahl verlustleistungsbedingter Redesigns, die aufgrund eines zu hohen Energieverbrauchs der Schaltung durchgeführt werden müssen. Bereits heute übersteigt die Leistungsdichte integrierter Schaltungen die von glühenden Herdplatten (siehe Bild 8). Ohne signifikante Verbesserung der Entwurfsverfahren würde die Leistungsdichte sehr bald die eines Kernreaktors oder gar einer Raketendüse erreichen. Aufgrund der wachsenden Zahl und Komplexität mobiler Systeme sind nicht nur aus ökologischen Gründen Maßnahmen zur Reduzierung der Energiedichte erforderlich. Am Beispiel des Mobiltelefons bedeutet dies eine Reduktion der Leistungsaufnahme um 50% im Normal-Betrieb und um 70% im Stand-by-Modus. Der Verbraucher bemerkt

**Bild 8** Dargestellt ist die Energiedichte auf Chips über die Zeit: Bereits heute übersteigt die Leistungsdichte integrierter Schaltungen die von glühenden Herdplatten. Ohne signifikante Verbesserung der Entwurfsverfahren würde die Leistungsdichte sehr bald die eines Kernreaktors oder gar einer Raketendüse erreichen. Für den kühlenden Lüfter ist das nicht zu schaffen.

den Erfolg durch eine deutlich gesteigerte aktive Sprechzeit von bis zu 20 Stunden und eine verbesserte Erreichbarkeit über 1000 Stunden. In den konkreten Anwendungsdomänen ist es das Ziel von LEMOS, die für die Fahrzeugsicherung relevanten Bordgeräte eines Kraftfahrzeugs aus der Batterie drei Monate operativ zu erhalten, sowie die Leistungsaufnahme von Mobiltelefonen um mehr als 50% zu senken.

Die technische Entwicklung von Systemen in der Nanotechnologie führt zu neuen Herausforderungen: Konnten noch vor ein paar Jahren die parasitären Eigenschaften von Leitungen vernachlässigt werden, so können diese heute das Verhalten der Schaltung dominieren. Dafür sorgen die drastisch steigenden Leitungslängen auf hochintegrierten Chips. Das kann soweit führen, dass nach bestehenden Regeln korrekt entworfene Schaltungen nicht funktionsfähig sind. Es kommt zu Re-Designs, die erhebliche Kosten verursachen, und das Erreichen der angestrebten technischen Ziele sehr erschweren. Ziel von LEONIDAS+ (Leitbahnorientiertes Design applikationsspezifischer Schaltungen) ist die Erarbeitung von Lösungen für die Extraktion, die Analyse und Modellierung der Leitbahneigenschaften für SoCs. Die Vorhersagbarkeit der physikalischen Eigenschaften eines SoC-Entwurfs wird damit bereits in einem sehr frühen Stadium mit hoher Genauigkeit gewährleistet. Bisher separate Entwurfsschritte laufen mit neuartigen Algorithmen simultan ab, sodass ein fehlerfreier Erstentwurf möglich ist. Konkret werden kompatible Leitbahn-Constraints, hochgenaue Referenzsimulationen zur Kalibrierung von Crosstalk-Problemen, die Behandlung von Prozessschwankungen auf Layoutebene, Kopplung von Substrat- und Leitbahnmodellierung, Timing-getriebene 3D-Platzierer für ICV, simultane Synthese und Platzierung von Leitbahnsystemen sowie automatisierte Berücksichtigung von Antiskew-Elementen bei der DfT-Prüfketten-Sortierung entwickelt.

Halbleiterprozesse im sub-100nm-Bereich erlauben bereits heute die monolithische Integration von komplexen mikroelektronischen Systemen auf einem Chip (SoC). Neben dem rasanten Wachstum der integrierbaren digitalen Signalverarbeitungsfunktionen entwickeln sich besonders analoge und mixedsignal Funktionalitäten zum Grundbestandteil solcher Systeme. Darüber hinaus steigt die Heterogenität

dieser Systeme durch die zunehmende Integration von sensorischen und mikromechanischen Funktionen sowie der Bereitstellung von Schnittstellenfunktionen zur Leistungselektronik und Hochfrequenztechnik rasch an. Die sich daraus unmittelbar ableitenden technischen Herausforderungen sind zur Bedienung der Nachfrage effizient zu lösen. Eine wesentliche Voraussetzung für die wirtschaftlich erfolgreiche Produktion im Markt für SoC ist die Verfügbarkeit von effizienten Testmethoden, die den ständig steigenden Anforderungen an die Zuverlässigkeit und Fehlerfreiheit gerecht werden. Hierbei ist es besonders wichtig, dass die Testmethoden unter industriellen Randbedingungen bei der Produktentwicklung und Chipherstellung wirtschaftlich und einfach anzuwenden sind. Das Projekt AZTEKE (Applikationsspezifische Testmethodik für hochkomplexe Systeme der Kommunikations- und Kraftfahrzeugtechnik) arbeitet insbesondere an der Verbesserung der Kostensituation beim Testen neuer Technologien mit einer Wafergröße von 300 mm Durchmesser. Auf diese können zweieinhalb Mal so viele Chips als auf einem 200 mm-Wafer aufgebracht werden, was eine Einsparung der Herstellungskosten von etwa 30% erbringt. Die Herausforderung auf dem Gebiet des Testens solcher (Logik-) Chips besteht darin, den gesamten Prüfaufwand für 300 mm-Wafer mit nicht mehr Aufwand an Testquipment und Zeit als bei 200 mm-Scheiben abzuwickeln. In AZTEKE werden innovative Testmethoden und neue Fehlermodelle für SoCs und Schaltungen mit mehreren Millionen Gattern entwickelt, die schnellere, effizientere und kostengünstigere Testmöglichkeiten für Pfadverzögerungen, Signalintegritätsverletzungen und Deterministic Logic Builtin Self-Test (DLBIST) bieten.

### 5 EDA-Clusterforschung

Ziel der Aktivitäten der EDA-Clusterforschung ist es, die EDA- Kompetenz in Bereichen, die für die deutsche Industrie bedeutend sind, durch die Durchführung von universitären Forschungsprojekten aufzubauen und zu verstärken. Universitäten und Forschungseinrichtungen erhalten in EDA-Clusterforschungsprojekten die Möglichkeit, neue Lösungen für EDA-Methoden und Verfahren zu erforschen, die in 5-10 Jahren in der Industrie zum Einsatz kommen können. Damit werden "Forschungscluster" gebildet und dem Netzwerk neue Impulse gegeben, um das Design-Gap in Zukunft weiter zu reduzieren. EDA-Clusterforschungsprojekte sind Projekte, in denen Hochschulen und Forschungseinrichtungen an zukunftsweisenden EDA-Forschungsthemen unter industrieller Patenschaft arbeiten. Aktuell werden vom edacentrum zwei Clusterforschungsprojekte be-

Im Projekt SAMS (Struktursynthese analoger Schaltungen) besteht die besondere Herausforderung darin, erstmalig zu praktikablen Lösungsvorschlägen im Bereich analoger Schaltungen zu kommen. Sie bewegen sich im Spannungsfeld zwischen einem vollständig neuen Aufbau aus Einzeltransistoren und der geschickten Verwendung und Modifikation existierender Module. Das Projektziel reicht weit über derzeitige Arbeiten zur Entwurfsautomatisierung hinaus, die sich vor allem mit den Aufgaben Dimensionierung und Wiederverwendung befassen. Das Konsortium treibt dabei die Vernetzung der unterschiedlichen Einzellösungen voran, um eine geschlossene Methodik anbieten zu können. In enger Zusammenarbeit mit industriellen Partnern werden neue Entwurfstechnologien erforscht und validiert, um dadurch signifikante Beiträge zur Top-Down-Synthese analoger Schaltungsstrukturen zu leisten. Der Analogentwurf ist durch eine Vielzahl von anwendungsspezifischen Entwurfsmethoden mit sehr unterschiedlichen Problemklassen gekennzeichnet. Je nachdem, ob z.B. einfache Operationsverstärker, Phasenregelschleifen, analog/digitale Blöcke wie Analog/Digital-Wandler oder komplexe Mixed-Signal-Systeme zu behandeln sind, werden während des Entwurfs unterschiedliche Abstraktionsebenen und Beschreibungsdomänen durchlaufen, für die verschiedene Modellierungssprachen verwendet werden. Dabei findet - meist auf der Architekturebene - auch der wichtige Übergang von nicht-konservativen (Flussgrößen) auf konservative, d.h. elektrische Signale statt. Es ergeben sich die drei Hierarchien, die zur Partitionierung der Syntheseschritte geeignet sind, die Systemebene, die Architekturebene und die elektrische Ebene. Das Projekt hat sich zum Ziel gesetzt, Lösungen aufzuzeigen, um diese Ebenen zu verbinden.

Mit der Verifikationsproblematik beschäftigt sich das Projekt FEST (Funktionale Verifikation von Systemen). Es hat sich zum Ziel gesetzt, Lösungen zu erforschen, die eine einheitliche Verifikation von SoCs ermöglichen. Hierzu werden von einer Systembeschreibung bis hinunter zur elektrischen Ebene Methoden und Verfahren erforscht, die existierende Verifikationslücken schließen. Dazu werden neue Verifikationsverfahren erforscht, die in der industriellen Praxis als große Hürde zu sehen sind. Die verschiedenen Verifikationsansätze werden auf einer gemeinsamen Plattform integriert, um eine einheitliche Verifikationsmethodik zu ermöglichen, aber unabhängig von einzelnen Lösungswerkzeugen zu bleiben.

Langfristig werden die innovativen EDA-Clusterforschungsprojekte einen zusätzlichen Antrieb für neue industrielle Fortschungsprojekte darstellen. Die daraus entwickelten technischen Lösungen sowie die innovative Struktur für die Kooperationen mit Clusterung der Hochschulen, einer zentralen Organisation durch das edacentrum und der Einbindung von und in F&E-Projekte(n) lassen für die deutsche Nanoelektronik-Zukunft hoffen.

#### 6 Fazit

Es gibt viel zu tun, um die Designfähigkeit angesichts des rasanten Forschritts der Halbleitertechnologie aufrechtzuerhalten. Die Gründung des edacentrum hat ein Netzwerk entstehen lassen, von dem alle Beteiligten profitieren. Die Tatsache, dass die Basistechnologie Nanoelektronik entscheidend zur Sicherung von Arbeitsplätzen – insbesondere in den Bereichen Automotive und Telekommunikation – beiträgt, stärkt ihre Bedeutung und damit auch die der Entwurfsautomatisierung.

#### Literatur

- [1] edacentrum, www.edacentrum.de

- [2] D. Treytnar, J. Haase: Neuer Schwung für EDA in Deutschland, Elektronik, Nr. 19/2002, S. 106–114.

- [3] D. Treytnar, R. Popp, J. Haase: EDA-Forschung in Deutschland, Elektronik, Nr. 25/2003, S. 88–94.

- [4] D. Treytnar, R. Popp: Nanoelektronik schafft Mobilität, Elektronik, Nr. 26/2004, S. 24–26.

- [5] edaKalender des edacentrum, http://www.edacentrum.de/edaKalender/

- [6] Ekompass Workshop, http://www.edacentrum.de/ekompass/ workshop/

- [7] edaForum, http://www.edacentrum.de/edaforum/

- http://www.edacentrum.de/edaatlas/

1 Dr.-Ing. Dieter Treytnar studierte an der Universität Hannover Elektrotechnik Fachrichtung Mikroelektronik. Von 1996 bis 2002 war er wissenschaftlicher Mitarbeiter am Institut für Theoretische Elektrotechnik in Hannover. Schwerpunkt seiner Arbeit war die Untersuchung der Signalausbreitung auf Leitungen sowie Entwicklung und Test von Systems-on-a-Chip . Er promovierte mit dem Thema "Einfluss parasitärer Effekte von Leitungssystemen der Nanoelektronik auf die Qualität von digitalen Testmustern". Seit Februar 2002 ist er im edacentrum Mitarbeiter für Öffentlichkeitsarbeit.

Adresse: edacentrum GmbH, Schneiderberg 32, 30167 Hannover,

E-Mail: treytnar@edacentrum.de

2 Dipl.-Ing. Ralf Popp studierte an der Universität Hannover Elektrotechnik Fachrichtung Mess- und Regelungstechnik. Von 1997 bis 2002 war er wissenschaftlicher Mitarbeiter am Institut für Mikroelektronische Systeme bei Professor Dr.-Ing. Erich Barke. Dort befasste er sich unter anderem mit Entwurfsverfahren für analoge und gemischt analog/digitale Schaltungen. Seine Dissertation zum Thema "Automatisierte symbolische Analyse nichtlinearer analoger Schaltungen" ist derzeit in Arbeit. Seit April 2002 ist er im edacentrum verantwortlich für die Öffentlichkeitsarbeit.

Adresse: edacentrum GmbH, Schneiderberg 32, 30167 Hannover, E-Mail: popp@edacentrum.de